# **Logic Design**

إعداد وتجميع ا<u>م</u>د/ هانى احمد عطاالله كلية الهندسة بقنا قسم الهندسة الكهربية

> العام الجامعي 2025/2024

# بيانات الكتاب

الكلية: الحاسبات والمعلومات الفرقة: المستوى الثانى التخصص: عام تاريخ النشر: 2024 عدد الصفحات: 145 اعداد وتجميع : ا.م. د/ هانى احمد عطاالله

الرموز المستخدمة

| Contents                                               | Page |

|--------------------------------------------------------|------|

| Introduction                                           | 5    |

| Ch1: Introduction to digital design and Binary Numbers | 9    |

| Ch1: Binary Codes and Logic Gates                      | 20   |

| Ch2: Boolean Algebra                                   | 39   |

| Ch2:Logic Gates and operations                         | 50   |

| Ch3: the map method and Gate Level Minimization        | 61   |

| Ch3: Nand and Nor Implementation                       | 82   |

| Ch4: Adders                                            | 91   |

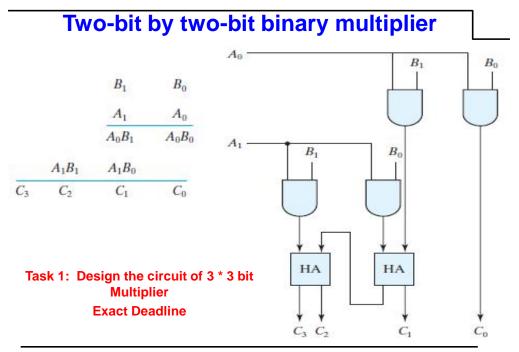

| Ch4: Multipliers                                       | 95   |

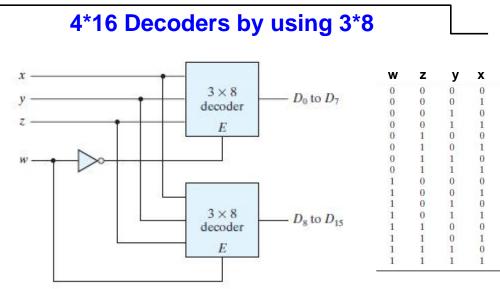

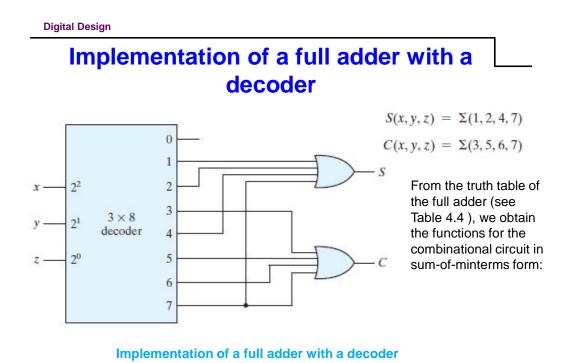

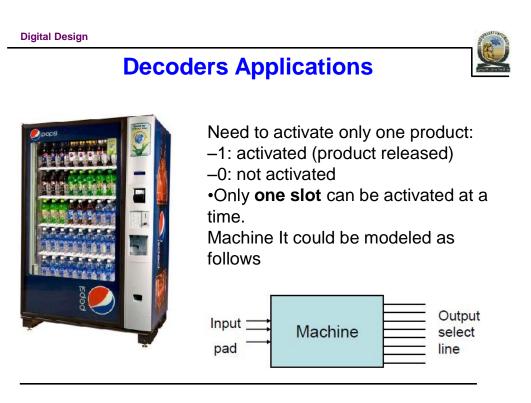

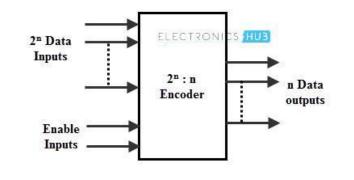

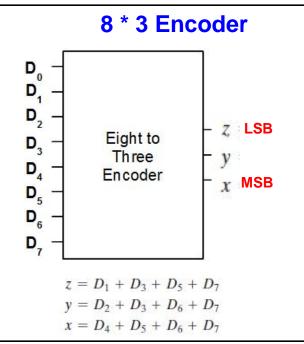

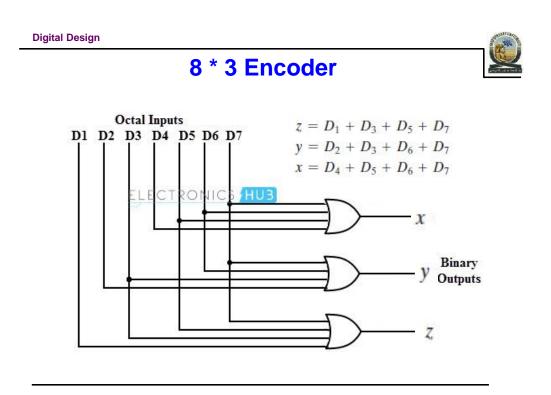

| Ch4: Decoders and Encoders                             | 106  |

| Ch4: Multiplexers                                      | 113  |

| Ch5: Sequential Circuits -Filp-Flops                   | 119  |

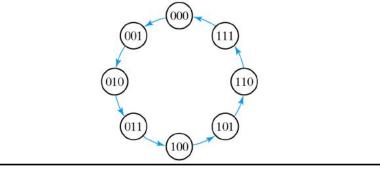

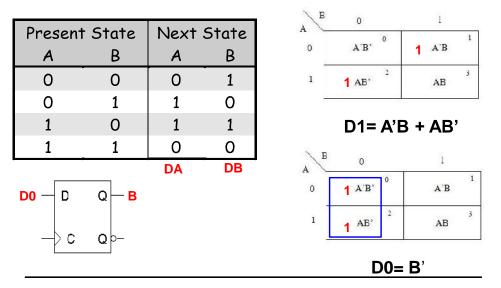

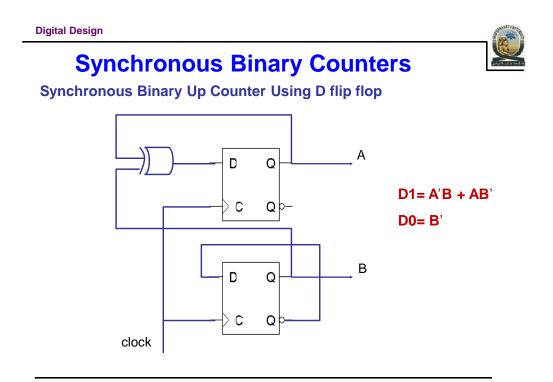

| Ch5: Sequential Circuits -Counters                     | 129  |

| Ch5: Registers and Shift registers                     | 142  |

| Ch5: Serial Addition and Ripple counters               | 145  |

| Review                                                 | 142  |

| References                                             | 145  |

# الصور والاشكال

# Introduction

Digital Design is about designing in digital space so that the created contents can be displayed and seen on a digital device. With the availability of high computing power, designers are able to quickly create designs in digital space prior to actual deployment.

The course is an introduction to digital design technology. It allows you to understand the basics of digital design and helps you develop skills.

In this course the student will be learn the following topics: Binary systems and Boolean algebra- logic gates – simplifying the Boolean circuit-combinational circuits- encryption and decryption - asynchronous sequential circuits and their applications- synchronous sequential circuits and their applicationsdisplacement recorders- counters – memories and types of memories.

The following is a brief summary of the topics that are covered in each chapter.

**Chapter 1** presents the various binary systems suitable for representing information in digital systems. The binary number system is explained and binary codes are illustrated. Examples are given for addition and subtraction of signed binary numbers and decimal numbers in binary-coded decimal (BCD) format.

**Chapter 2** introduces the basic postulates of Boolean algebra and shows the correlation between Boolean expressions and their corresponding logic diagrams. All Possible logic operations for two variables are investigated, and the most useful logic gates used in the design of digital systems are identified. This chapter also introduces basic CMOS logic gates.

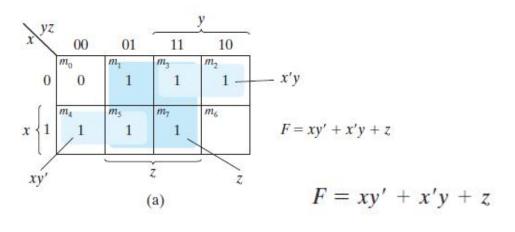

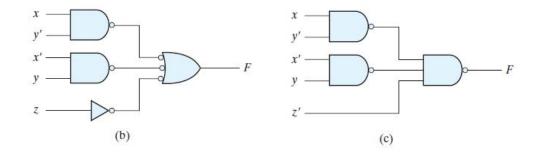

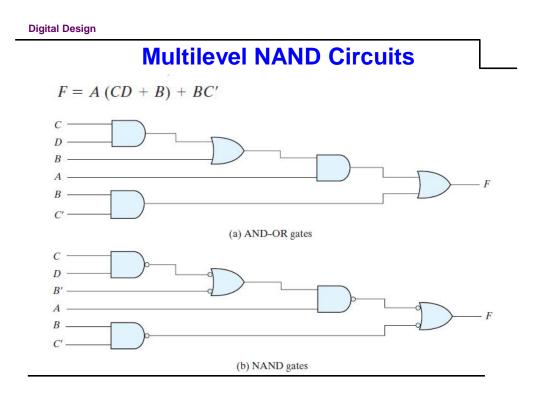

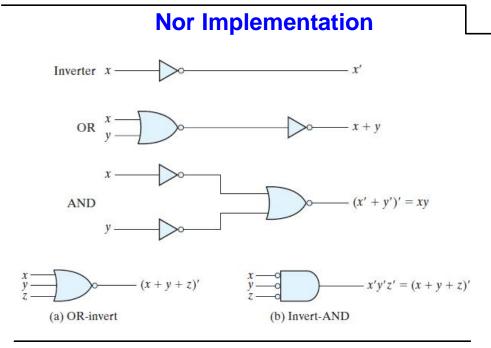

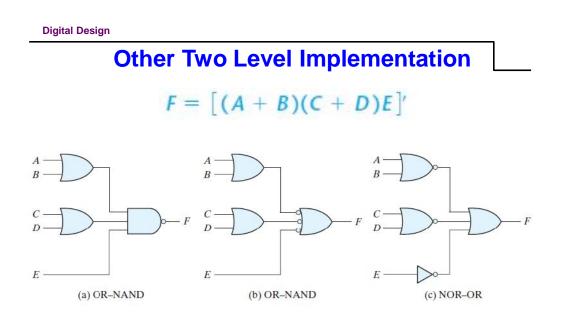

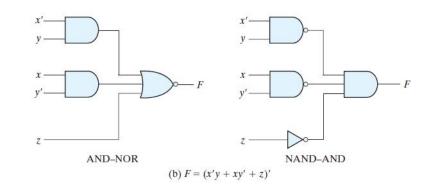

**Chapter 3** covers the map method for simplifying Boolean expressions. The map method is also used to simplify digital circuits constructed with AND-OR, NAND, or NOR gates. All other possible two-level gate circuits are considered, and their method of implementation is explained. Verilog HDL is introduced together with simple examples of gate-level models.

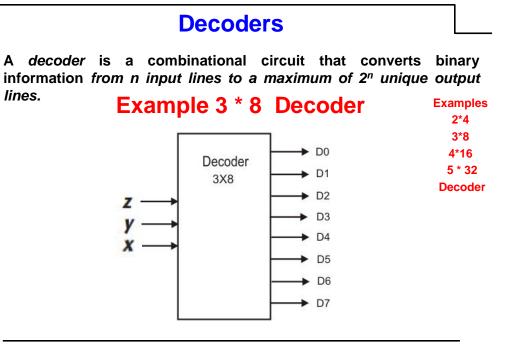

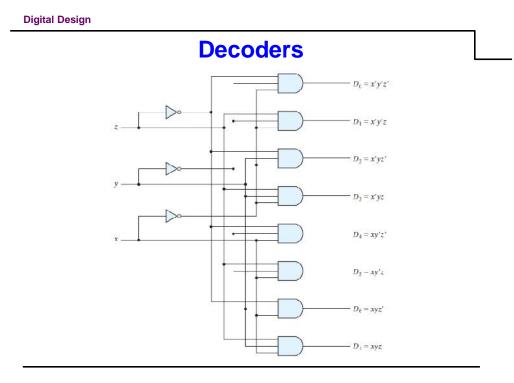

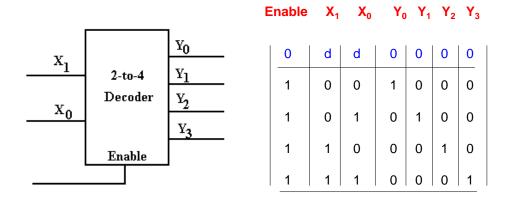

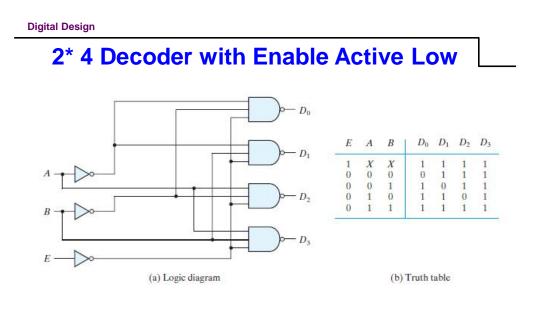

**Chapter 4** outlines the formal procedures for the analysis and design of combinational circuits. Some basic components used in the design of digital systems, such as adders and code converters, are introduced as design examples. Frequently used digital logic functions such as parallel adders and subtractors, decoders, encoders, and multiplexers are explained, and their use in the design of combinational circuits is illustrated.

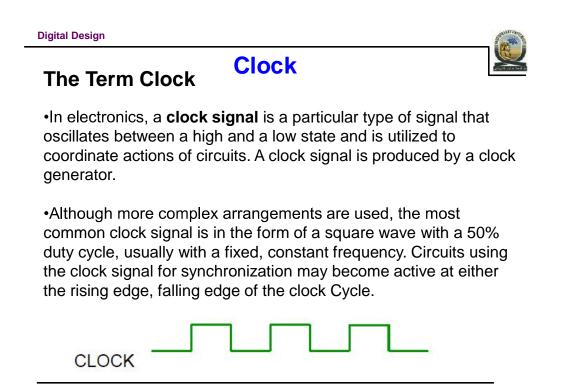

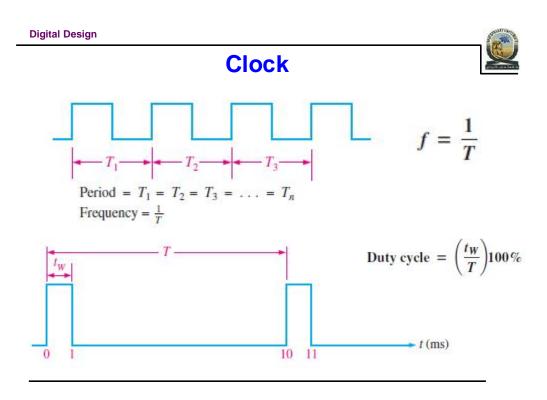

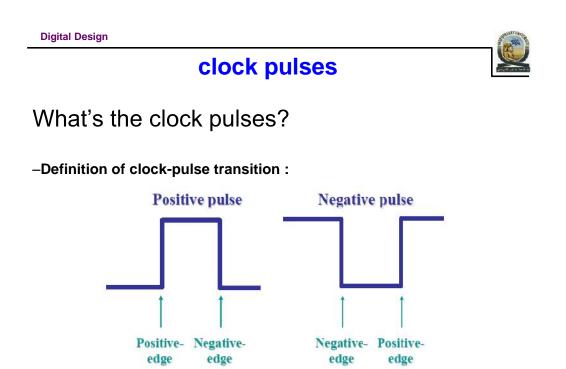

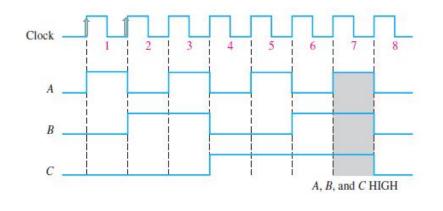

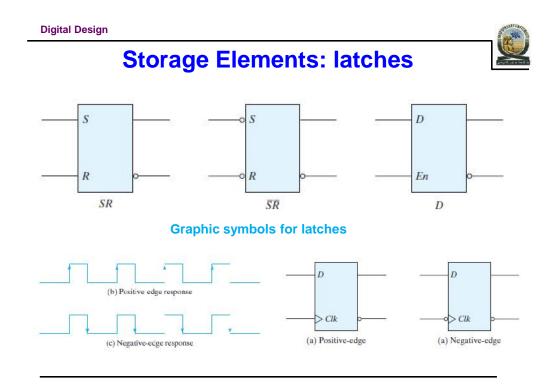

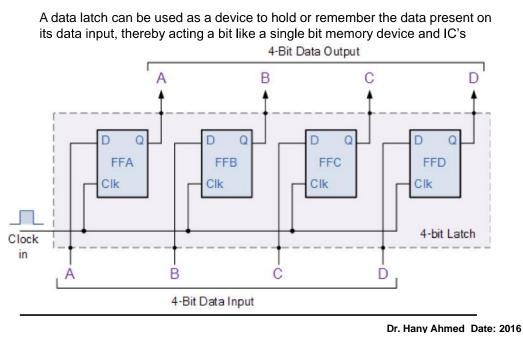

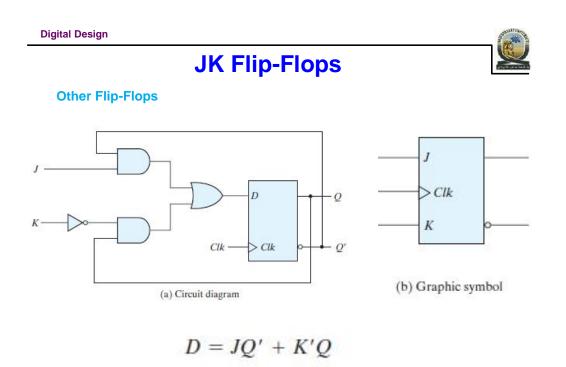

**Chapter 5** outlines the formal procedures for analyzing and designing clocked (synchronous) sequential circuits. The gate structure of several types of flip-flops is presented together with a discussion on the difference between level and edge triggering.

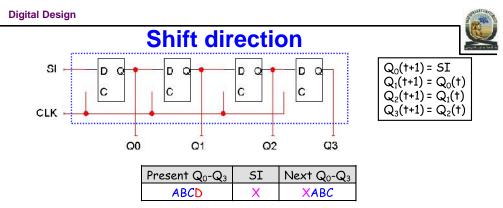

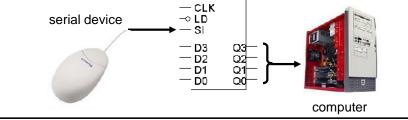

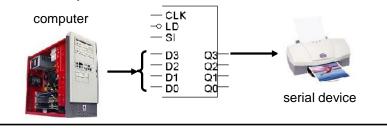

**Chapter 6** deals with various sequential circuit components such as registers, shift registers, and counters. These digital components are the basic building blocks from which more complex digital systems.

# Logic Design

## **Table of Contents**

| Week1   | Ch1: Introduction to digital design and Binary<br>Numbers |

|---------|-----------------------------------------------------------|

| Week2   | Ch1: Binary Codes and Logic Gates                         |

| Week3   | Ch2: Boolean Algebra                                      |

| Week4   | Ch2:Logic Gates and operations                            |

| Week5   | <b>Ch3: the map method and Gate Level</b><br>Minimization |

| Week6   | Ch3: Nand and Nor Implementation                          |

| Week7   | Ch4: Adders                                               |

| Week8   | Ch4: Multipliers                                          |

| Week9   | Midterm Exam                                              |

| Week10  | Ch5: Decoders and Encoders                                |

| Week 11 | Ch5: Multiplixers                                         |

| Week 12 | Ch6: Sequential Circuits -Filp-Flops                      |

| Week 13 | Ch6: Sequential Circuits -Counters                        |

| Week14  | Ch7: Registers and Shift registers                        |

| Week 15 | Ch7: Serial Addition and Ripple counters                  |

| Week 16 | Review                                                    |

# Ch1: Introduction to Digital Design and Binary Numbers

## **Digital vs. Analog**

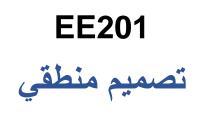

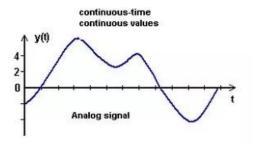

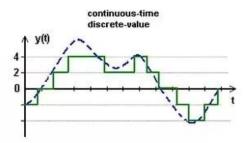

Analog: Continuous function V of continuous variable t (time, space etc.) : V(t)

An analog\* quantity is one having continuous values.

Example: Human voice in air, analog devices.

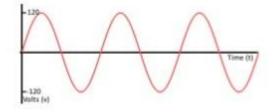

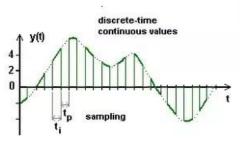

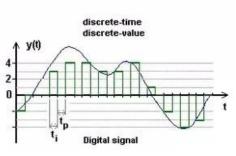

**Digital**: Discrete function Vk of discrete sampling variable tk, with k = integer: Vk = V(tk) A digital quantity is one having a discrete set of values.

## **Continuous vs. Discrete**

## Continuous:

- > defined for every instant of time

- $\blacktriangleright$  denoted by x(t)

## Discrete:

defined at the discrete-instant of time

## **Digital vs. Analog**

- An analog system has continuous range of values

- [ A mercury thermometer

- **Vinyl records**

- [ Human eye

- A digital system has a set of discrete values

- [ Digital Thermometer

- [ Compact Disc (CD)

- Digital camera

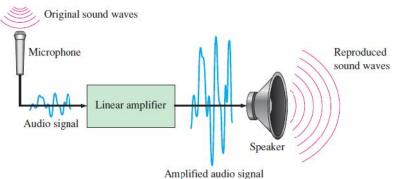

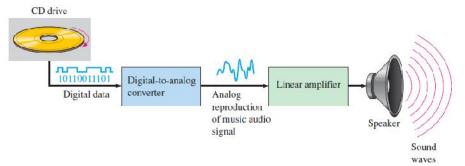

- Analog System: Audio System

## System using Digital and Analog Methods: The Compact Disk (CD) Player

## **Digital Systems and Units**

## **Benefits of using digital**

- Advantages of using Digital:

- Cheap electronic circuits

- Easier to calibrate and adjust

- Resistance to noise: Clearer picture and sound

## **Data Types and Representation**

1- Integers: 35, 125, 5612\*1e2

2-Real Numbers, 5.67, 0.05, 52\*1e0.5

3-Strings, a- Names (ali, maha, ...) b- Dates (12/9/2016) c- Addresses (Qena, Egypt) d- Telephone Numbers (0965214264) e- string: \$, &,%,@,...

**Digital Design**

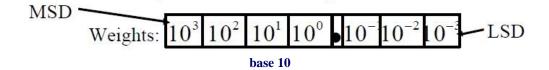

## **Number Systems : 1- Decimal Code**

Base (Radix) is 10 - symbols (0,1, . . 9) Digits (Base-1)

✓ If we were to write 1936.25 using a power series expansion and **base 10** arithmetic:

$$1 \times 10^{3} + 9 \times 10^{2} + 3 \times 10^{1} + 6 \times 10^{0} + 2 \times 10^{-1} + 5 \times 10^{-2}$$

# 2- Binary Number System

Discrete elements of information are represented with bits called *binary codes*.

- Base is 2 symbols (0,1) Binary Digits (Bits)

- Each position carries a weight (using decimal).

MSD Weights:

$$2^3 2^2 2^1 2^0 2^{-1} 2^{-2} 2^{-3}$$

LSD

✓ If we write 10111.01 using a decimal power series we convert from binary to decimal:

$1 \times 2^{4} + 0 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0} + 0 \times 2^{-1} + 1 \times 2^{-2} =$ =1×16 + 0×8 +1×4 +1×2 +1×1+ 0× 0.5 +1× 0.25 = 23.25

**Digital Design**

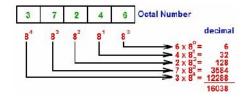

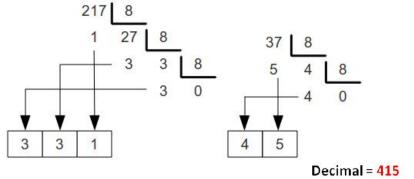

## **3- Octal Number system**

The octal number system [from Greek: OKT $\Omega$ ]. - Its base is 8  $\rightarrow$  eight digits 0, 1, 2, 3, 4, 5, 6, 7

✓

$$(236.4)8 = (?)10$$

2×8<sup>2</sup> + 3×8<sup>1</sup> + 6×8<sup>0</sup> + 4×8<sup>-1</sup> = 158.5

# 4- Hexadecimal Number system

-The hexadecimal number system [from Greek:  $\Delta EKAE\XiI$ ].

- Its base is  $16 \rightarrow$  first 10 digits are borrowed from the decimal system (0 -- 9) and the letters A, B, C, D, E, F are used for the digits 10, 11, 12, 13, 14, 15

$$\checkmark$$

(D63FA)<sub>16</sub> = (?)<sub>10</sub>

$13 \times 16^4 + 6 \times 16^3 + 3 \times 16^2 + 15 \times 16^1 + 10 \times 16^0 = 877562$

Hexadecimal

(base 16)

A B

C D

E

F

## **Digital Design**

### **Different Systems** Numbers with Different Bases Decimal Binary Octal (base 2) (base 10) (base 8)

## **Conversion from Binary to Decimal**

Let each bit of a binary number be represented by a variable whose subscript = bit positions, i.e.,

$(110)_2 = (a_2 a_1 a_0)_2$

Its decimal equivalent is:

$(1 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0})_{10} = (a_{2} \times 2^{2} + a_{1} \times 2^{1} + a_{0} \times 2^{0})_{10}$

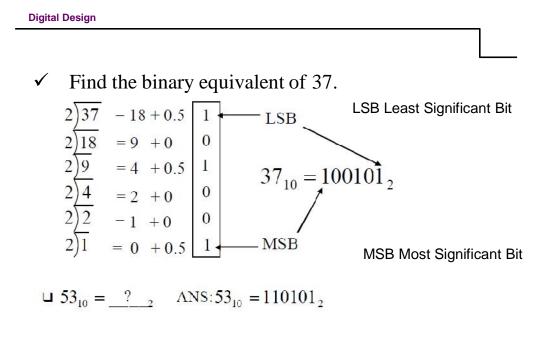

It is necessary to separate the number into an integer part and a fraction: Repeatedly divide the decimal number by 2.

**Digital Design**

## **Conversion from decimal fraction to binary:**

same method used for integers except multiplication is used instead of division.

✓ Convert  $(0.8542)_{10}$  to binary (give answer to 6 digits).

$(0.8542)_{10} = (0.a_{-1}a_{-2}a_{-3}a_{-4}a_{-5}a_{-6})_2 = (0.110110)_2$

Dr. Hany Ahmed Date: 9/2017

```

Digital Design

```

Convert  $(0.6875)_{10}$  to binary. First, 0.6875 is multiplied by 2 to give an integer and a fraction. Then the new fraction is multiplied by 2 to give a new integer and a new fraction. The process is continued until the fraction becomes 0 or until the number of digits has sufficient accuracy. The coefficients of the binary number are obtained from the integers as follows:

|                     | Integer |   | Fraction | Coefficient  |

|---------------------|---------|---|----------|--------------|

| 0.6875 × 2 =        | 1       | + | 0.3750   | $a_{-1} = 1$ |

| $0.3750 \times 2 =$ | 0       | + | 0.7500   | $a_{2} = 0$  |

| $0.7500 \times 2 =$ | 1       | + | 0.5000   | $a_{-3} = 1$ |

| $0.5000 \times 2 =$ | 1       | + | 0.0000   | $a_{-4} = 1$ |

| Division | Quotient | Remainder |

|----------|----------|-----------|

| 415/8    | 51       | 7         |

| 51/8     | 6        | 3         |

| 6/8      | 0        | 6         |

Octal = 637

Dr. Hany Ahmed Date: 9/2017

## **Digital Design**

Conversion from Decimal to Octal

Decimal to Octal Conversion

Example: (175)10

|                                | Quoti | ent F   | Remainder                         | Coefficient                                                                    |

|--------------------------------|-------|---------|-----------------------------------|--------------------------------------------------------------------------------|

| 175 / 8 =                      | 2     | 1       | 7                                 | $a_0 = 7$                                                                      |

| 21 / 8 =                       | 2     |         | 5                                 | $a_1 = 5$                                                                      |

| 2 / 8 =                        | 0     |         | 2                                 | $a_2 = 2$                                                                      |

| Ans                            | swer: | (17     | 75) <sub>10</sub> = (a            | <sub>2</sub> a <sub>1</sub> a <sub>0</sub> ) <sub>8</sub> = (257) <sub>8</sub> |

| Example: (0.3125) <sub>1</sub> | 0     |         |                                   |                                                                                |

|                                | 1     | Integer | Fraction                          | Coefficient                                                                    |

| 0.3125 *                       | * 8 = | 2       | . 5                               | $a_{.1} = 2$                                                                   |

| 0.5 *                          | 8 =   | 4       | . 0                               | $a_{.2} = 4$                                                                   |

| Answer:                        | (0.3  | 125)1   | <sub>0</sub> = (0.a <sub>-1</sub> | a <sub>-2</sub> a <sub>-3</sub> ) <sub>8</sub> = (0.24) <sub>8</sub>           |

**Digital Design**

## **Conversion from decimal fraction to Octal:**

Convert  $(0.513)_{10}$  to octal.

$0.513 \times 8 = 4.104$   $0.104 \times 8 = 0.832$   $0.832 \times 8 - 6.656$   $0.656 \times 8 = 5.248$   $0.248 \times 8 = 1.984$  $0.984 \times 8 = 7.872$

The answer, to seven significant figures, is obtained from the integer part of the products:

$(0.513)_{10} = (0.406517...)_8$

Dr. Hany Ahmed Date: 9/2017

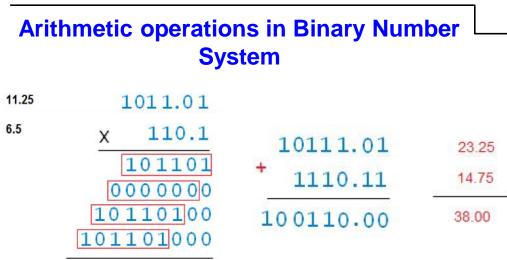

# Arithmetic operations in Systems Arithmetic operations in Binary Number System

| augend: | 101101  | minuend:    | 101101  | multiplicand: | 1011         |

|---------|---------|-------------|---------|---------------|--------------|

| addend: | +100111 | subtrahend: | -100111 | multiplier:   | $\times$ 101 |

| sum:    | 1010100 | difference: | 000110  |               | 1011         |

|         |         |             |         | L             | > 0000       |

|         |         |             | part    | ial product:  | ≥ 1011       |

|         |         |             |         | product:      | 110111       |

Dr. Hany Ahmed Date: 9/2017

73.125

Dr. Hany Ahmed Date: 9/2017

Digital Design

# Arithmetic operations in Octal Number System

## Evaluate:

(i) (162)<sub>8</sub> + (537)<sub>8</sub>

1001001.001

11 <---- carry 162 <u>537</u> 721

Therefore, sum =  $(721)_8$

# Arithmetic operations in Octal Number System

(iv) (67.5) <sub>8</sub> + (45.6) <sub>8</sub>

## Solution:

1 1 <---- carry 67.5 <u>45.6</u> 135.3 Therefore, sum = (135.3) <sub>8</sub>

**Digital Design**

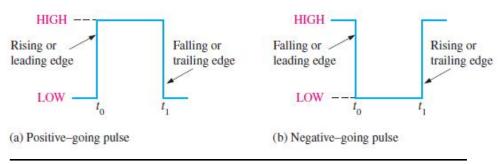

# **Binary Digits**

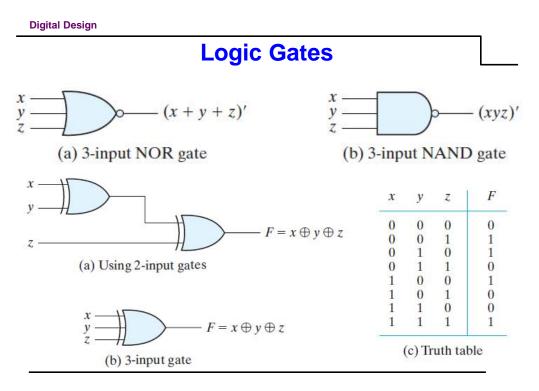

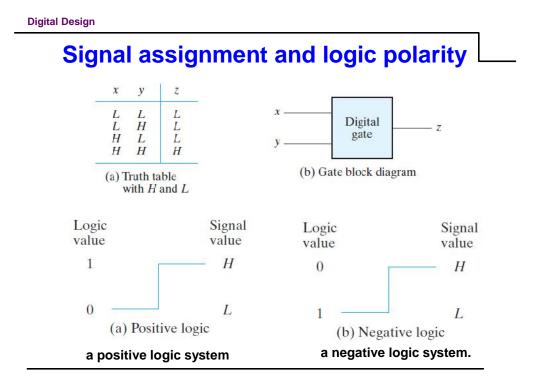

Each of the two digits in the **binary** system, 1 and 0, is called a **bit**, which is a contraction of the words *binary digit*. In digital circuits, two different voltage levels are used to represent the two bits. Generally, 1 is represented by the higher voltage, which we will refer to as a HIGH, and a 0 is represented by the lower voltage level, which we will refer to as a LOW. This is called **positive logic** and will be used throughout the book.

## HIGH 1 and LOW 0

| (          |                               |                |

|------------|-------------------------------|----------------|

| 1024 bytes | = 1 KB                        | KB = Kilobyte  |

| 1024 KB    | = 1 MB                        | MB = Megabyte  |

| 1024 MB    | = 1 GB                        | GB = Gigabyte  |

| 1024 GB    | = 1 TB                        | TB = Terabyte  |

| 1024 TB    | = 1 PB                        | PB = Petabyte  |

|            | 1024 KB<br>1024 MB<br>1024 GB | 1024 GB = 1 TB |

## **Systematic multiples**

the International System of Units (SI).

| roystem |        | · · ·                                | memory standards                    | JEDEC               |

|---------|--------|--------------------------------------|-------------------------------------|---------------------|

| Symbol  | Prefix | SI Meaning                           | Binary meaning                      | memory<br>standards |

| k       | kilo   | $10^3 = 1000^1$                      | 2 <sup>10</sup> = 1024 <sup>1</sup> | otanidardo          |

| M       | mega   | $10^6 = 1000^2$                      | 2 <sup>20</sup> = 1024 <sup>2</sup> |                     |

| G       | giga   | $10^9 = 1000^3$                      | 2 <sup>30</sup> = 1024 <sup>3</sup> |                     |

| т       | tera   | 10 <sup>12</sup> = 1000 <sup>4</sup> | 2 <sup>40</sup> = 1024 <sup>4</sup> |                     |

| P       | peta   | 10 <sup>15</sup> = 1000 <sup>5</sup> | 2 <sup>50</sup> = 1024 <sup>5</sup> |                     |

| E       | exa    | 10 <sup>18</sup> = 1000 <sup>6</sup> | 2 <sup>60</sup> = 1024 <sup>6</sup> |                     |

| Z       | zetta  | $10^{21} = 1000^7$                   | 2 <sup>70</sup> = 1024 <sup>7</sup> |                     |

| Y       | yotta  | 10 <sup>24</sup> = 1000 <sup>8</sup> | 2 <sup>80</sup> = 1024 <sup>8</sup> |                     |

Joint Electron Device Engineering Council (JEDEC)

## **Digital Design**

## **ASCII Code**

|                                       | ASCII Code                 | :      |

|---------------------------------------|----------------------------|--------|

| An alphanumeric                       | 0 0011 0000                | 0      |

| character /a a latter or              | 1 0011 0001                | P      |

| character (e.g. a letter or           | 2 0011 0010                | Q      |

| number such as 'A', 'B'               | 3 0011 0011                | R      |

| number such as A, D                   | 4 0011 0100                | S      |

| or '7') is stored as 1 byte.          | 5 0011 0101                | T      |

|                                       | • •••••                    | U      |

| For example, to store the             |                            | v      |

| • •                                   | 8 0011 1000                | W      |

| letter 'R' uses 1 byte,               |                            | x      |

|                                       | A 0100 0001                | Y      |

| which is stored by the                | B 0100 0010                | z      |

| computer as 8 bits,                   | C 0100 0011                | a<br>b |

| computer as o bits,                   | D 0100 0100<br>E 0100 0101 | c      |

| '01010010'.                           | -                          | a      |

|                                       | G 0100 0111                | e      |

| ASCII (American                       | H 0100 1000                | £      |

| · · · · · · · · · · · · · · · · · · · | I 0100 1001                | g      |

| Standard Code for                     | J 0100 1010                | h      |

| Information Interchange)              | K 0100 1011                | I      |

| Information Interchange)              | L 0100 1100                | j      |

| Code                                  | M 0100 1101                | k      |

| COUC                                  | N 0100 1110                | 1      |

|                                       |                            |        |

| ASCII | Code: | Character | to | Binary |

|-------|-------|-----------|----|--------|

|       |       |           |    |        |

| 0 | 0011 | 0000 | 0 | 0100 | 1111 | m     | 0110 | 1101 |  |

|---|------|------|---|------|------|-------|------|------|--|

| 1 | 0011 | 0001 | P | 0101 | 0000 | n     | 0110 | 1110 |  |

| 2 | 0011 | 0010 | Q | 0101 | 0001 | 0     | 0110 | 1111 |  |

| 3 | 0011 | 0011 | R | 0101 | 0010 | P     | 0111 | 0000 |  |

| 4 | 0011 | 0100 | s | 0101 | 0011 | q     | 0111 | 0001 |  |

| 5 | 0011 | 0101 | т | 0101 | 0100 | r     | 0111 | 0010 |  |

| 6 | 0011 | 0110 | σ | 0101 | 0101 | s     | 0111 | 0011 |  |

| 7 | 0011 | 0111 | v | 0101 | 0110 | t     | 0111 | 0100 |  |

| 8 | 0011 | 1000 | w | 0101 | 0111 | u     | 0111 | 0101 |  |

| 9 | 0011 | 1001 | x | 0101 | 1000 | v     | 0111 | 0110 |  |

| A | 0100 | 0001 | Y | 0101 | 1001 | w     | 0111 | 0111 |  |

| в | 0100 | 0010 | z | 0101 | 1010 | x     | 0111 | 1000 |  |

| C | 0100 | 0011 | a | 0110 | 0001 | У     | 0111 | 1001 |  |

| D | 0100 | 0100 | b | 0110 | 0010 | z     | 0111 | 1010 |  |

| E | 0100 | 0101 | c | 0110 | 0011 |       | 0010 | 1110 |  |

| F | 0100 | 0110 | a | 0110 | 0100 | ,     | 0010 | 0111 |  |

| G | 0100 | 0111 | e | 0110 | 0101 |       | 0011 | 1010 |  |

| н | 0100 | 1000 | £ | 0110 | 0110 | ,     | 0011 | 1011 |  |

| I | 0100 | 1001 | g | 0110 | 0111 | 7     | 0011 | 1111 |  |

| J | 0100 | 1010 | h | 0110 | 1000 | 1     | 0010 | 0001 |  |

| ĸ | 0100 | 1011 | I | 0110 | 1001 |       | 0010 | 1100 |  |

| L | 0100 | 1100 | j | 0110 | 1010 | -     | 0010 | 0010 |  |

| м | 0100 | 1101 | k | 0110 | 1011 | (     | 0010 | 1000 |  |

| N | 0100 | 1110 | 1 | 0110 | 1100 | )     | 0010 | 1001 |  |

|   |      |      |   |      |      | space | 0010 | 0000 |  |

# **Complements of Numbers**

Why?  $\rightarrow$  to simplify the subtraction operation

There are two types of complements for each base<sup>-</sup>r system: the radix complement and the diminished radix complement. The first is referred to as the r's complement and the second as the (r - 1)>s

complement. When the value of the base *r* is substituted in the name.

the two types are referred to as **the 2's complement** and **1's complement** for binary numbers and the 10's complement and 9's complement for

decimal numbers.

## **Digital Design**

# **Complements of Numbers**

The (r - 1)>s complement.

The 9's complement of 546700 is 999999 - 546700 = 453299. The 9's complement of 012398 is 999999 - 012398 = 987601.

The 1's complement of 1011000 is 0100111.

The 1's complement of 0101101 is 1010010.

## Invert the binary digits

# Complements of Numbers The r's complement. the 10's complement of 012398 is 987602 and the 10's complement of 012398 is 987602 and The 9's complement of 012398 is 987602 and The 9's complement of 246700 is 753300 The 9's complement + 1 Or the 10's complement of the first digit then the 9's for the reaming digits. the 2's complement of 1101100 is 0010100 and the 2's complement of 0110111 is 1001001 The 1's complement + 1 Or keep the first One (not the first digit) from left then Invert all digits (after).

## **Digital Design**

## **Subtraction with Complements**

The subtraction of two *n*-digit unsigned numbers M - N in base *r* can be done as follows:

- 1. Add the minuend M to the r's complement of the subtrahend N. Mathematically,  $M + (r^n - N) = M - N + r^n$ .

- 2. If  $M \ge N$ , the sum will produce an end carry  $r^n$ , which can be discarded; what is left is the result M N.

- 3. If M < N, the sum does not produce an end carry and is equal to  $r^n (N M)$ , which is the r's complement of (N M). To obtain the answer in a familiar form, take the r's complement of the sum and place a negative sign in front.

The following examples illustrate the procedure:

## **Subtraction with Complements**

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a) X - Y and (b) Y - X by using 2's complements.

| (a) | X = 1010100                         | 84 |

|-----|-------------------------------------|----|

|     | 2's complement of $Y = + 0111101$   | 67 |

|     | Sum = 10010001                      |    |

|     | Discard end carry $2^7 = -10000000$ |    |

|     | <i>Answer</i> : $X - Y = 0010001$   | 17 |

## **Digital Design**

## **Subtraction with Complements**

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a) X - Y and (b) Y - X by using 2's complements.

(b) Y = 10000112's complement of X = + 0101100Sum = 1101111

There is no end carry. Therefore, the answer is Y - X = -(2>s complement of 1101111) = -0010001

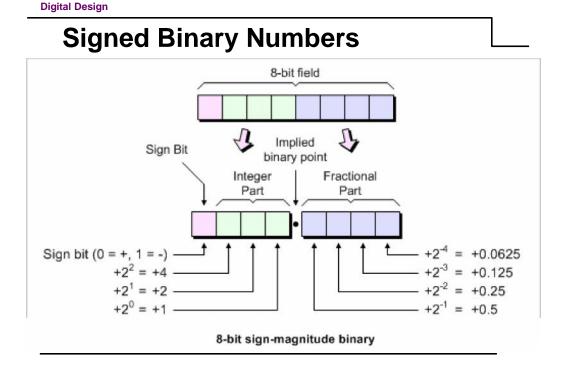

# Signed Binary Numbers 1- the signed-magnitude

The representation: the sign with a bit placed in the leftmost position of the number. The convention is to make the sign **bit 0** for **positive** and **1** for **negative**.

For example, the string of bits 01001 can be considered as 9 (unsigned binary) or as +9 (signed binary)

The string of bits 11001 represents the binary equivalent of 25 when considered as an unsigned number and the binary equivalent of -9 when considered as a signed number

referred to as the signed-magnitude

## **Signed Binary Numbers** Most Significant Bit Least Significant Bit Bit (MSB) (LSB) 1 0 0 0 1 1 0 1 0 0 SIGN BIT DATA WORD **16-bit Sign-magnitude Binary**

## **Digital Design**

## 2- the signed-Complement system

The complement will always start with a 1, indicating a negative number. The signed-complement system can use either the 1's or the 2's complement, but the 2's complement is the most common.

## there are three different ways to represent -9 with eight bits

| signed-magnitude representation: -9   | 10001001        |

|---------------------------------------|-----------------|

| signed-1's-complement representation: | <u>11110110</u> |

| signed-2's-complement representation: | 11110111        |

# Signed Binary Numbers

| Decimal | Signed-2's<br>Complement | Signed-1's<br>Complement | Signed<br>Magnitude |

|---------|--------------------------|--------------------------|---------------------|

| +7      | 0111                     | 0111                     | 0111                |

| +6      | 0110                     | 0110                     | 0110                |

| +5      | 0101                     | 0101                     | 0101                |

| 14      | 0100                     | 0100                     | 0100                |

| +3      | 0011                     | 0011                     | 0011                |

| +2      | 0010                     | 0010                     | 0010                |

| +1      | 0001                     | 0001                     | 0001                |

| +0      | 0000                     | 0000                     | 0000                |

| -0      |                          | 1111                     | 1000                |

| -1      | 1111                     | 1110                     | 1001                |

| 2       | 1110                     | 1101                     | 1010                |

| -3      | 1101                     | 1100                     | 1011                |

| -4      | 1100                     | 1011                     | 1100                |

| -5      | 1011                     | 1010                     | 1101                |

| -6      | 1010                     | 1001                     | 1110                |

| 7       | 1001                     | 1000                     | 1111                |

| -8      | 1000                     |                          | -                   |

## **Digital Design**

# **Arithmetic Addition**

|     |          | Discard | d Carry  |

|-----|----------|---------|----------|

| + 6 | 00000110 | - 6     | 11111010 |

| +13 | 00001101 | +13     | 00001101 |

| +19 | 00010011 | + 7     | 00000111 |

| + 6 | 00000110 | - 6     | 11111010 |

| -13 | 11110011 | -13     | 11110011 |

| - 7 | 11111001 | -19     | 11101101 |

# **Arithmetic Subtraction**

Take the 2's complement of the subtrahend (including the sign bit) and add it to the minuend (including the sign bit). A carry out of the sign-bit position is discarded.

> $(\pm A) - (+B) = (\pm A) + (-B);$  $(\pm A) - (-B) = (\pm A) + (+B).$

consider the subtraction (-6) - (-13) = +7.

written as (11111010 - 11110011).

The subtraction is changed to addition by taking the 2's complement of the subtrahend (-13), giving (+13).

11111010 + 00001101 = 100000111. Removing the end carry, we obtain the correct answer: 00000111 (+7).

## **Digital Design**

# Why Signed Binary Numbers

It is worth noting that binary numbers in the signed complement system are added

and subtracted by the same basic addition and subtraction rules as unsigned numbers.

Therefore, computers need only one common hardware circuit to handle both types of

**arithmetic.** This consideration has resulted in the signed complement system being used

in virtually all arithmetic units of computer systems.

Dr. Hany Ahmed Date: 9/2017

# **Binary Coded Decimal-BCD**

each decimal digit is represented by its corresponding four-bit binary value

| Decimal digit |   | B | CD |   |

|---------------|---|---|----|---|

| Decimal digit | 8 | 4 | 2  | 1 |

| 0             | 0 | 0 | 0  | 0 |

| 1             | 0 | 0 | 0  | 1 |

| 2             | 0 | 0 | 1  | 0 |

| 3             | 0 | 0 | 1  | 1 |

| 4             | 0 | 1 | 0  | 0 |

| 5             | 0 | 1 | 0  | 1 |

| 6             | 0 | 1 | 1  | 0 |

| 7             | 0 | 1 | 1  | 1 |

| 8             | 1 | 0 | 0  | 0 |

| 9             | 1 | 0 | 0  | 1 |

the binary combinations 1010 through 1111 are not used and have no meaning in BCD.

$(185)_{10} = (0001\ 1000\ 0101)_{BCD} = (10111001)_2$

an advantage in the use of decimal numbers, because computer input and output data are generated by people who use the decimal system.

## **Digital Design**

# **BCD Addition**

| 4  | 0100  | 4  | 0100  | 8  | 1000  |

|----|-------|----|-------|----|-------|

| +5 | +0101 | +8 | +1000 | +9 | 1001  |

| 9  | 1001  | 12 | 1100  | 17 | 10001 |

|    |       |    | +0110 |    | +0110 |

|    |       |    | 10010 |    | 10111 |

# **BCD Addition**

| BCD        | 1     | 1     |      |      |

|------------|-------|-------|------|------|

|            | 0001  | 1000  | 0100 | 184  |

|            | +0101 | 0111  | 0110 | +576 |

| Binary sum | 0111  | 10000 | 1010 |      |

| Add 6      |       | 0110  | 0110 |      |

| BCD sum    | 0111  | 0110  | 0000 | 760  |

Dr. Hany Ahmed Date: 2017

## **Digital Design**

# **Different Binary Codes**

| Decimal<br>Digit | BCD<br>8421 | 2421 | Excess-3 | 8, 4, -2, -1 |

|------------------|-------------|------|----------|--------------|

| 0                | 0000        | 0000 | 0011     | 0000         |

| 1                | 0001        | 0001 | 0100     | 0111         |

| 2                | 0010        | 0010 | 0101     | 0110         |

| 3                | 0011        | 0011 | 0110     | 0101         |

| 4                | 0100        | 0100 | 0111     | 0100         |

| 5                | 0101        | 1011 | 1000     | 1011         |

| 6                | 0110        | 1100 | 1001     | 1010         |

| 7                | 0111        | 1101 | 1010     | 1001         |

| 8                | 1000        | 1110 | 1011     | 1000         |

| 9                | 1001        | 1111 | 1100     | 1111         |

|                  | 1010        | 0101 | 0000     | 0001         |

| Unused           | 1011        | 0110 | 0001     | 0010         |

| bit              | 1100        | 0111 | 0010     | 0011         |

| combi-           | 1101        | 1000 | 1101     | 1100         |

| nations          | 1110        | 1001 | 1110     | 1101         |

|                  | 1111        | 1010 | 1111     | 1110         |

**Digital Design**

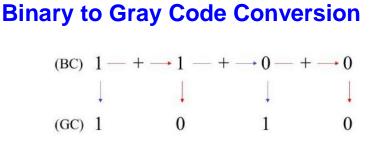

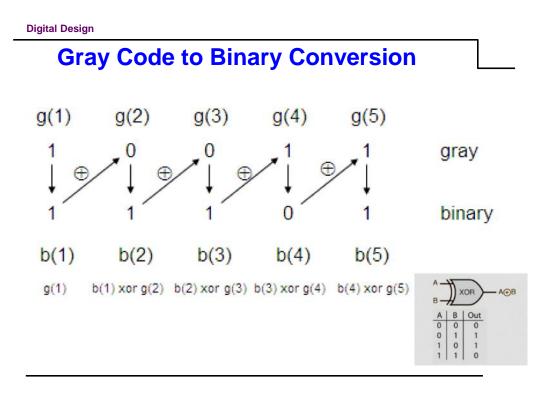

# **Gray Code**

The reflected binary code (RBC)

advantage of the Gray code over the straight binary number sequence is that only one bit in the code group changes in going from one number to the next.

| Decimal | Binary | Gray | Gray as decimal |

|---------|--------|------|-----------------|

| 0       | 000    | 000  | 0               |

| 1       | 001    | 001  | 1               |

| 2       | 010    | 011  | 3               |

| 3       | 011    | 010  | 2               |

| 4       | 100    | 110  | 6               |

| 5       | 101    | 111  | 7               |

| 6       | 110    | 101  | 5               |

| 7       | 111    | 100  | 4               |

Dr. Hany Ahmed Date: 2017

| Gray Code                                      |      |                       |

|------------------------------------------------|------|-----------------------|

|                                                | Gray | Decimal<br>Equivalent |

| he <b>reflected binary code</b> ( <b>RBC</b> ) | Code | Equivalent            |

|                                                | 0000 | 0                     |

|                                                | 0001 | 1                     |

|                                                | 0011 | 23                    |

|                                                | 0010 |                       |

|                                                | 0110 | 4<br>5                |

|                                                | 0111 | 5                     |

|                                                | 0101 | 6                     |

|                                                | 0100 | 7                     |

|                                                | 1100 | 8                     |

|                                                | 1101 | 9                     |

|                                                | 1111 | 10                    |

|                                                | 1110 | 11                    |

|                                                | 1010 | 12                    |

|                                                | 1011 | 13                    |

|                                                | 1001 | 14                    |

|                                                | 1000 | 15                    |

- · MSB does not change as a result of conversion

- Start with MSB of binary number and add it to neighboring binary bit to get the next Gray code bit

- Repeat for subsequent Gray coded bits

Dr. Hany Ahmed Date: 2017

Dr. Hany Ahmed Date: 2017

## **ASCII Character Code**

American Standard Code for Information Interchange (ASCII)

|          |      |     |     | b7t | 6b5 |          |     |     |

|----------|------|-----|-----|-----|-----|----------|-----|-----|

| b4b3b2b1 | 000  | 001 | 010 | 011 | 100 | 101      | 110 | 111 |

| 0000     | NUL. | DLE | SP  | 0   | @   | Р        | 15  | р   |

| 0001     | SOH  | DC1 | !   | 1   | A   | Q        | a   | q   |

| 0010     | STX  | DC2 | "   | 2   | В   | R        | b   | г   |

| 0011     | FTX  | DC3 | #   | 3   | С   | S        | с   | S   |

| 0100     | EOT  | DC4 | \$  | 4   | D   | Т        | d   | t   |

| 0101     | ENO  | NAK | %   | 5   | E   | U        | e   | u   |

| 0110     | ACK  | SYN | &   | 6   | F   | V        | f   | v   |

| 0111     | BEL  | ETB | 4   | 7   | G   | W        | g   | w   |

| 1000     | BS   | CAN | (   | 8   | Н   | X        | h   | X   |

| 1001     | HT   | EM  | )   | 9   | 1   | Y        | i   | у   |

| 1010     | LF   | SUB | *   | :   | J   | Z        | j   | Z   |

| 1011     | VT   | ESC | +   | ;   | K   | [        | k   | ſ   |

| 1100     | FΓ   | FS  |     | <   | L   | <i>V</i> | 1   | È   |

| 1101     | CR   | GS  | -   | =   | M   | ]        | ш   | }   |

| 1110     | SO   | RS  |     | >   | N   | A        | n   |     |

| 1111     | SI   | US  | 1   | ?   | 0   | 1000     | o   | DEL |

Dr. Hany Ahmed Date: 2017

## **Digital Design**

# **Error-Detecting Code**

A *parity bit* is an extra bit included with a message to make the total number of 1's either even or odd.

Even Parity Check  $\rightarrow$ 1- No. of One's Even  $\rightarrow$  0 2- No. of One's Odd $\rightarrow$  1

|                     | With even parity | With odd parity   |

|---------------------|------------------|-------------------|

| ASCII $A = 1000001$ | 01000001         | 11000001          |

| ASCII T = 1010100   | 11010100         | 01010100          |

| Odd Parity Check →  | The parity       | hit is helpful in |

1- No. of One's Even  $\rightarrow$  1 2- No. of One's Odd $\rightarrow$  0 The parity bit is helpful in detecting errors during the transmission of information

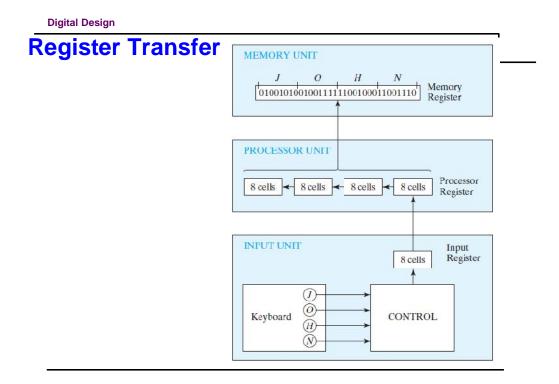

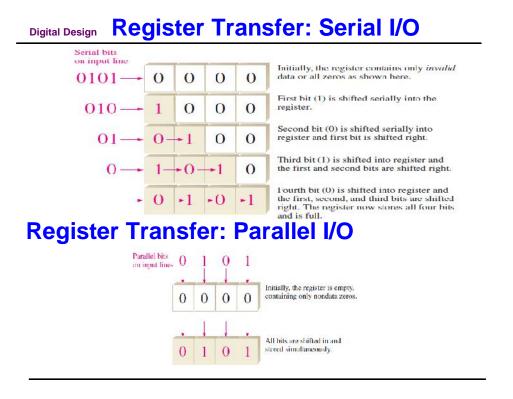

## **BINARY STORAGE AND REGISTERS**

# **Registers**

A *register* is a group of binary cells. A register with *n* cells can store any discrete quantity of information that contains *n* bits.

A register with 16 cells can be in one of 2<sup>16</sup> possible states

# **Register Transfer**

is a basic operation that consists of a transfer of binary information from one set of registers into another set of registers.

Dr. Hany Ahmed Date: 2017

Dr. Hany Ahmed Date: 2017

## **Digital Design**

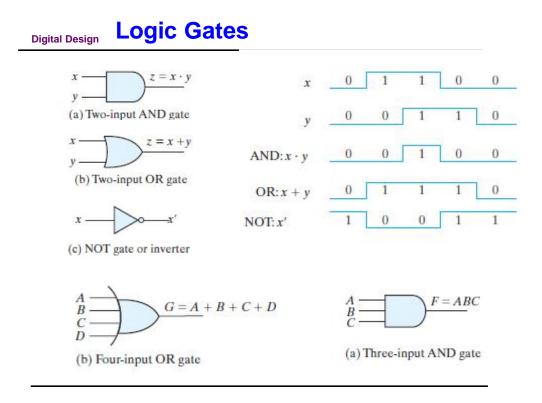

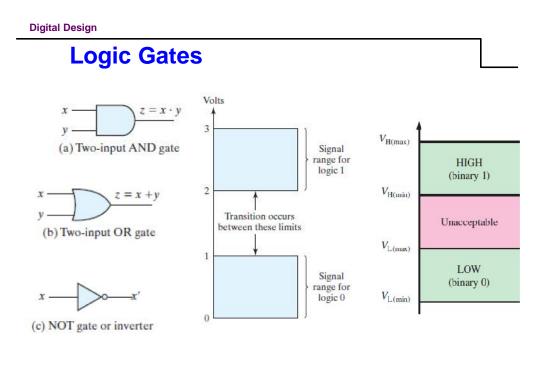

## **BINARY LOGIC**

Binary logic consists of binary variables and a set of logical operations. The variables are designated by letters of the alphabet, such as A, B, C, x, y, z, etc., with each variable having two and only two distinct possible values: 1 and 0. There are three basic logical operations:

Truth Tables of Logical Operations

AND, OR, and NOT.

| AND |   | AND OR      |   |   |                     | NOT |    |  |

|-----|---|-------------|---|---|---------------------|-----|----|--|

| x   | y | $x \cdot y$ | x | y | <i>x</i> + <i>y</i> | x   | x' |  |

| 0   | 0 | 0           | 0 | 0 | 0                   | 0   | 1  |  |

| 0   | 1 | 0           | 0 | 1 | 1                   | 1   | 0  |  |

| 1   | 0 | 0           | 1 | 0 | 1                   |     |    |  |

| 1   | 1 | 1           | 1 | 1 | 1                   |     |    |  |

Dr. Hany Ahmed Date: 2017

## Digital Design CH 2 : Boolean Algebra and Logic Gates Boolean Algebra

- (a) The structure is closed with respect to the operator +.

(b) The structure is closed with respect to the operator ·.

- 2. (a) The element 0 is an identity element with respect to +; that is, x + 0 = 0 + x = x.

- (b) The element 1 is an identity element with respect to  $\cdot$ ; that is,  $x \cdot 1 = 1 \cdot x = x$ .

- 3. (a) The structure is commutative with respect to +; that is, x + y = y + x.

(b) The structure is commutative with respect to •; that is, x y = y x.

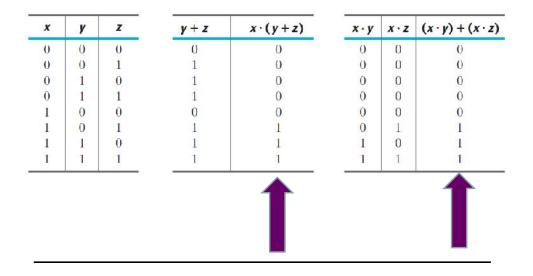

- 4. (a) The operator · is distributive over +; that is, x · (y + z) = (x · y) + (x · z).

(b) The operator + is distributive over ·; that is, x + (y · z) = (x + y) · (x + z).

- 5. For every element  $x \in B$ , there exists an element  $x' \in B$  (called the *complement* of x) such that (a) x + x' = 1 and (b)  $x \cdot x' = 0$ .

- 6. There exist at least two elements  $x, y \in B$  such that  $x \neq y$ .

Dr. Hany Ahmed Date: 2017

| Digital Design                                                   | Boolean Alg                  | jebra              |

|------------------------------------------------------------------|------------------------------|--------------------|

| $\frac{\text{ldentity}}{0 + x} =$                                | = <i>x</i>                   | $1 \cdot x = x$    |

| $\begin{array}{l} \text{Commutation} \\ x \cdot y = \end{array}$ |                              | x + y = y + x      |

| <b>Distribution</b> $x \cdot (y + z) =$                          |                              |                    |

| $x + (y \cdot z) =$<br>Complement                                | $(x + y) \cdot (x + x') = 1$ | $(x \cdot x') = 0$ |

## **Boolean Algebra**

Dr. Hany Ahmed Date: 2017

#### **Digital Design**

## **Basic Theorems**

## **Duality**

Postulates and Theorems of Boolean Algebra

| Postulate 2               | (a) | x + 0 = x                 | (b) | $x \cdot 1 = x$         |

|---------------------------|-----|---------------------------|-----|-------------------------|

| Postulate 5               | (a) | x + x' = 1                | (b) | $x \cdot x' = 0$        |

| Theorem 1                 | (a) | x + x = x                 | (b) | $x \cdot x = x$         |

| Theorem 2                 | (a) | x + 1 = 1                 | (b) | $x \cdot 0 = 0$         |

| Theorem 3, involution     |     | (x')' = x                 |     |                         |

| Postulate 3, commutative  | (a) | x + y = y + x             | (b) | xy = yx                 |

| Theorem 4, associative    | (a) | x + (y + z) = (x + y) + z | (b) | x(yz) = (xy)z           |

| Postulate 4, distributive | (a) | x(y+z) = xy + xz          | (b) | x + yz = (x + y)(x + z) |

| Theorem 5, DeMorgan       | (a) | (x + y)' = x'y'           | (b) | (xy)' = x' + y'         |

| Theorem 6, absorption     | (a) | x + xy = x                | (b) | x(x + y) = x            |

## **Basic Theorems**

**THEOREM 1(a):** x + x = x.

| Statement                 | Justification  |

|---------------------------|----------------|

| $x + x = (x + x) \cdot 1$ | postulate 2(b) |

| = (x+x)(x+x')             | 5(a)           |

| = x + xx'                 | 4(b)           |

| = x + 0                   | 5(b)           |

| = x                       | 2(a)           |

Dr. Hany Ahmed Date: 2017

Digital Design

**Basic Theorems**

**THEOREM 6(a):** x + xy = x.

| Statement                 | Justification  |

|---------------------------|----------------|

| $x + xy = x \cdot 1 + xy$ | postulate 2(b) |

| =x(1 + y)                 | 4(a)           |

| = x(y + 1)                | 3(a)           |

| $= x \cdot 1$             | 2(a)           |

| = x                       | 2(b)           |

| Digital D | Design |     | E             | Basic Th  | eor            | em         | S          |          |       |

|-----------|--------|-----|---------------|-----------|----------------|------------|------------|----------|-------|

| DeM       | org    | an  | 's <b>the</b> | orem      |                |            |            |          |       |

|           |        |     |               | (         | <i>x</i> +     | - y)       | )′=        | = x'     | y'    |

| Usin      | ng C   | )ua | lity          | De Morg   | an's           | Th         | eare       | m        |       |

|           |        |     |               | X.y = 7   | i + - <u>-</u> | II.        | > x        | ·y = 1   | X+Yo  |

|           |        |     |               | X · y = 7 | ۍ<br>تو . تړ   | =          | > ×        | +4 = 3   | IX IS |

|           |        |     |               |           |                |            |            | 1        | -     |

|           | x      | y   | x + y         | (x + y)'  |                | <b>x</b> ′ | <b>y</b> ' | x'y'     |       |

|           | 0      | 0   | 0             | 1         |                | 1          | 1          | 1        |       |

|           | 0      | 1   | 1             | 0         |                | 1          | 0          | 0        |       |

|           | 1      | 0   | 1             | 0         |                | 0          | 1          | 0        |       |

|           | 1      | 1   | 1             | 0         |                | 0          | 0          | 0        |       |

|           |        |     |               |           |                |            |            | <u>_</u> |       |

#### **Digital Design**

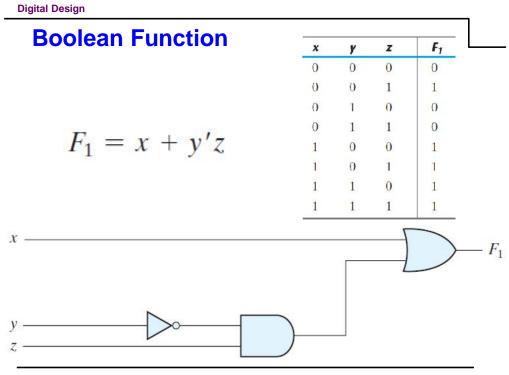

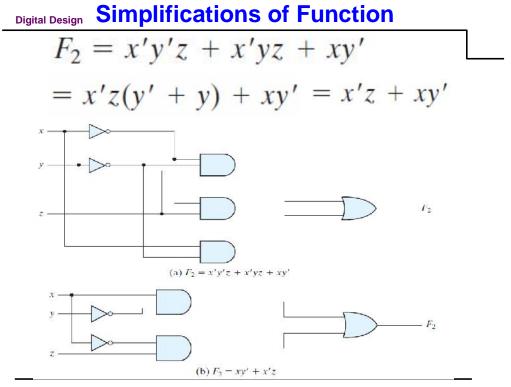

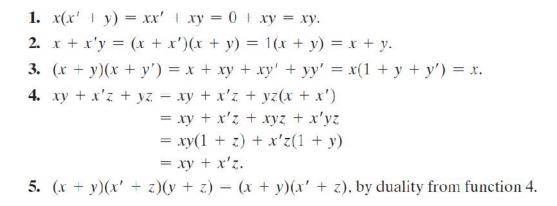

### **Simplifications of Function**

## **Complement of a Function**

The complement of a function *F* is *F*'

$$(A + B + C)' = (A + x)' \quad \text{let } B + C = x$$

= A'x' by theorem 5(a) (DeMorgan)

= A'(B + C)' substitute B + C = x

= A'(B'C') by theorem 5(a) (DeMorgan)

= A'B'C' by theorem 4(b) (associative)

Dr. Hany Ahmed Date: 2017

#### **Digital Design**

## **Complement of a Function**

### These theorems can be generalized as follows:

$$(A + B + C + D + \dots + F)' = A'B'C'D'\dots F'$$

$(ABCD\dots F)' = A' + B' + C' + D' + \dots + F'$

Find the complement of the functions  $F_1 = x'yz' + x'y'z$

$$F'_{1} = (x'yz' + x'y'z)' = (x'yz')'(x'y'z)'$$

=  $(x + y' + z)(x + y + z')$

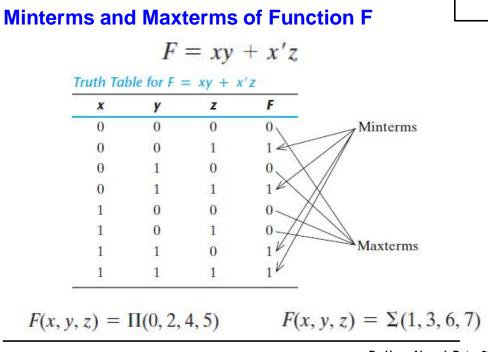

## **Canonical and Standard Forms**

### Minterms and Maxterms

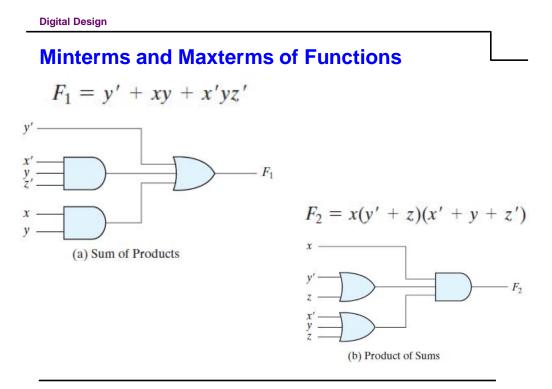

A Boolean function can be expressed algebraically from a given truth table by forming a minterm for each combination of the variables that produces a 1 in the function and then taking the OR of all those terms.

Minterms or Standard Products Function → (Sum of Product)

### Maxterms or Standard Sums Function $\rightarrow$ (Product of Sums)

Dr. Hany Ahmed Date: 2017

**Digital Design**

## **Canonical and Standard Forms**

### **Minterms and Maxterms**

Minterms and Maxterms for Three Binary Variables

|   |   |   | M      | interms     | Maxte        | rms         |

|---|---|---|--------|-------------|--------------|-------------|

| x | у | Z | Term   | Designation | Term         | Designation |

| 0 | 0 | 0 | x'y'z' | $m_0$       | x + y + z    | $M_0$       |

| 0 | 0 | 1 | x'y'z  | m           | x + y + z'   | $M_1$       |

| 0 | 1 | 0 | x'yz'  | $m_2$       | x + y' + z   | $M_2$       |

| 0 | 1 | 1 | x'yz   | $m_3$       | x + y' + z'  | $M_3$       |

| 1 | 0 | 0 | xy'z'  | $m_4$       | x' + y + z   | $M_4$       |

| 1 | 0 | 1 | xy'z   | $m_5$       | x' + y + z'  | $M_5$       |

| 1 | 1 | 0 | xyz'   | $m_6$       | x' + y' + z  | $M_6$       |

| 1 | 1 | 1 | xyz    | $m_7$       | x' + y' + z' | $M_7$       |

#### Hint: Minterms are the complements of the Maxterms or vice versa

### **Canonical and Standard Forms Minterms or Standard Products**

| ctio | ns of Th | ree Varia | 5 L                     | <i></i> )             | yz + xy'z      |   | , uj |

|------|----------|-----------|-------------------------|-----------------------|----------------|---|------|

| ĸ    | y        | z         | Function f <sub>1</sub> |                       | Function $f_2$ | - |      |

| )    | 0        | 0         | 0                       | <i>m</i> <sub>0</sub> | 0              |   |      |

| )    | 0        | 1         | 1                       | $m_1$                 | 0              |   |      |

| )    | 1        | 0         | 0                       | <i>m</i> <sub>2</sub> | 0              |   |      |

| )    | 1        | 1         | 0                       | <i>m</i> <sub>3</sub> | 1              |   |      |

| 1    | 0        | 0         | 1                       | $m_4$                 | 0              |   |      |

| 1    | 0        | 1         | 0                       | $m_5$                 | 1              |   |      |

| 1    | 1        | 0         | 0                       | m <sub>6</sub>        | 1              |   |      |

| 1    | 1        | 1         | 1                       | m <sub>7</sub>        | 1              |   |      |

Dr. Hany Ahmed Date: 2017

#### **Digital Design**

### **Canonical and Standard Forms Maxterms or Standard Sums**

For example

$f'_{1} = x'y'z' + x'yz' + x'yz + xy'z + xyz'$ The complement of  $f_1$  is read as

| $f_1 = (x + y +$ | z)(x + y' - | (x' + y + z)(x' + y + y) + (x' + y)(x' + y)(x' + y) + (x' + y)(x' + y)(x' + y)(x' + y)(x' + y)(x' + y) + (x' + y)(x' + y)( | z')(x' | + y' + z) |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|

|                  |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |           |

|   |   |   | Maxte        | erms        |

|---|---|---|--------------|-------------|

| x | y | z | Term         | Designation |

| 0 | 0 | 0 | x + y + z    | $M_0$       |

| 0 | 0 | 1 | x + y + z'   | $M_1$       |

| 0 | 1 | 0 | x + y' + z   | $M_2$       |

| 0 | 1 | 1 | x + y' + z'  | $M_3$       |

| 1 | 0 | 0 | x' + y + z   | $M_4$       |

| 1 | 0 | 1 | x' + y + z'  | $M_5$       |

| 1 | 1 | 0 | x' + y' + z  | $M_6$       |

| 1 | 1 | 1 | x' + y' + z' | $M_7$       |

### **Canonical and Standard Forms**

Boolean functions expressed as a sum of minterms or product of maxterms are said to be in *canonical form*.

The minterms whose sum defines the Boolean function are those which give the 1's of the function in a truth table

Express the Boolean function F = A + B'C as a sum of minterms. The function has three variables: A, B, and C. The first term A is missing two variables; therefore,

A = A(B + B') = AB + AB'

Dr. Hany Ahmed Date: 2017

**Digital Design**

### Example

Express the Boolean function F = A + B'C as a sum of minterms.

# The function has three variables: *A*, *B*, and *C*. The first term *A* is missing two variables; therefore,

$$A = A(B + B') = AB + AB'$$

This function is still missing one variable, so

$$A = AB(C + C') + AB'(C + C')$$

= ABC + ABC' + AB'C + AB'C'

The second term BC is missing one variable; hence,

$$B'C = B'C(A + A') = AB'C + A'B'C$$

Combining all terms, we have But AB'C appears twice (x + x = x)

$$F = A + B'C$$

= ABC + ABC' + AB'C + AB'C' + A'B'C

$$F = A'B'C + AB'C + AB'C + ABC' + ABC$$

=  $m_1 + m_4 + m_5 + m_6 + m_7$

$$F(A, B, C) = \Sigma(1, 4, 5, 6, 7)$$

The summation symbol stands for the ORing of terms

Dr. Hany Ahmed Date: 2017

#### **Digital Design**

### **Another solution**

An alternative procedure for deriving the minterms of a Boolean function is to obtain the truth table of the function directly from the algebraic expression and then read the minterms from the truth table.

| Truth | Table | for $F =$ | A + | B'C |

|-------|-------|-----------|-----|-----|

|       |       |           |     |     |

|   | F | C | B | Α |

|---|---|---|---|---|

| m | 0 | 0 | 0 | 0 |

| m | 1 | 1 | 0 | 0 |

| m | 0 | 0 | 1 | 0 |

| m | 0 | 1 | 1 | 0 |

| m | 1 | 0 | 0 | 1 |

| m | 1 | 1 | 0 | 1 |

| m | 1 | 0 | 1 | 1 |

| m | 1 | 1 | 1 | 1 |

$$F(A, B, C) = \Sigma(1, 4, 5, 6, 7)$$

### **Example : Maxterms**

Express the Boolean function  $F=xy+x^{\prime}z^{\prime}$  as a product of maxterms

$$F = xy + x'z = (xy + x')(xy + z)$$

=  $(x + x')(y + x')(x + z)(y + z)$

=  $(x' + y)(x + z)(y + z)$

The function has three variables: *x*, *y*, and *z*. Each OR term is missing one variable; therefore,

$$x' + y = x' + y + zz' = (x' + y + z)(x' + y + z')$$

$$x + z = x + z + yy' = (x + y + z)(x + y' + z)$$

$$y + z = y + z + xx' = (x + y + z)(x' + y + z)$$

Dr. Hany Ahmed Date: 2017

**Digital Design**

### **Example : Maxterms**

Express the Boolean function F=xy+x'z as a product of maxterms

$$F = (x + y + z)(x + y' + z)(x' + y + z)(x' + y + z')$$

=  $M_0 M_2 M_4 M_5$

$$F(x, y, z) = \Pi(0, 2, 4, 5)$$

The product symbol denotes the ANDing of maxterms

The maxterms whose product defines the Boolean function are those which give the 0's of the function in a truth table

### **Example : Maxterms**

Express the Boolean function F=xy+x'z as a product of maxterms

<u>Hint.</u> An alternative procedure for deriving the maxterms of a Boolean function is to obtain the truth table of the function directly from the algebraic expression and then read the maxterms from the truth table.

| x | Y | Z |       | F |

|---|---|---|-------|---|

| 0 | 0 | 0 | $M_0$ | 0 |

| 0 | 0 | 1 | $M_1$ | 1 |

| 0 | 1 | 0 | $M_2$ | 0 |

| 0 | 1 | 1 | $M_3$ | 1 |

| 1 | 0 | 0 | $M_4$ | 0 |

| 1 | 0 | 1 | $M_5$ | 0 |

| 1 | 1 | 0 | $M_6$ | 1 |

| 1 | 1 | 1 | $M_7$ | 1 |

$F(x, y, z) = \Pi(0, 2, 4, 5)$

Dr. Hany Ahmed Date: 2017

#### **Digital Design**

### **Conversion between Canonical Forms**

$$F(A, B, C) = \Sigma(1, 4, 5, 6, 7)$$

This function has a complement that can be expressed as

$$F'(A, B, C) = \Sigma(0, 2, 3) = m_0 + m_2 + m_3$$

Now, if we take the complement of F by DeMorgan's theorem, we obtain F in a different form:

$$F = (m_0 + m_2 + m_3)' = m'_0 \cdot m'_2 \cdot m'_3 = M_0 M_2 M_3 = \Pi(0, 2, 3)$$

$$m'_j = M_j$$

the maxterm with subscript j is a complement of the minterm with the same subscript j and vice versa.

## **Boolean Algebra and Logic Gates**

## 2.7 Other Logic Operations

| X | Y | Fo                                   | <b>F</b> 1 | F <sub>2</sub> | F <sub>3</sub> | F4 | F <sub>5</sub> | F <sub>6</sub> | F7 | <b>F</b> <sub>8</sub> | Fo | F10 | F <sub>11</sub> | F12 | <b>F</b> <sub>13</sub> | F14 | <b>F</b> 15 |

|---|---|--------------------------------------|------------|----------------|----------------|----|----------------|----------------|----|-----------------------|----|-----|-----------------|-----|------------------------|-----|-------------|

| 0 | 0 | 0                                    | 0          | 0              | 0              | 0  | 0              | 0              | 0  | 1                     | 1  | 1   | 1               | 1   | 1                      | 1   | 1           |

| 0 | 1 | 0                                    | 0          | 0              | 0              | 1  | 1              | 1              | 1  | 0                     | 0  | 0   | 0               | 1   | 1                      | 1   | 1           |

| 1 | 0 | <b>F</b> <sub>0</sub><br>0<br>0<br>0 | 0          | 1              | 1              | 0  | 0              | 1              | 1  | 0                     | 0  | 1   | 1               | 0   | 0                      | 1   | 1           |

| 1 | 1 | 0                                    | 1          | 0              | 1              | 0  | 1              | 0              | 1  | 0                     | 1  | 0   | 1               | 0   | 1                      | 0   | 1           |

Dr. Hany Ahmed Date: 2016

#### **Digital Design**

| Boolean Functions | Operator<br>Symbol | Name         | Comments             |  |  |

|-------------------|--------------------|--------------|----------------------|--|--|

| $F_0 = 0$         |                    | Null         | Binary constant 0    |  |  |

| $F_1 = xy$        | $x \cdot y$        | AND          | x and y              |  |  |

| $F_2 - xy'$       | <i>x/y</i>         | Inhibition   | x, but not y         |  |  |

| $F_3 = x$         |                    | Transfer     | X                    |  |  |

| $F_4 = x'y$       | y/x                | Inhibition   | y, but not $x$       |  |  |

| $F_5 = y$         |                    | Transfer     | у                    |  |  |

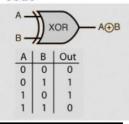

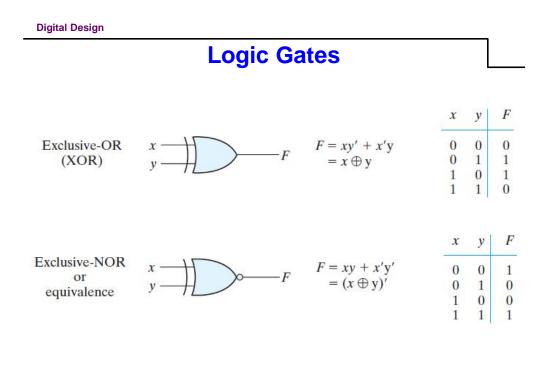

| $F_6 = xy' + x'y$ | x ① y              | Exclusive-OR | x or y, but not both |  |  |

| $F_7 = x + y$     | $x \perp y$        | OR           | x or y               |  |  |

| $F_8 = (x + y)'$  | $x \downarrow y$   | NOR          | Not-OR               |  |  |

| $F_9 = xy + x'y'$ | $(x \oplus y)'$    | Equivalence  | x equals y           |  |  |

| $F_{10} = y'$     | y'                 | Complement   | Not y                |  |  |

| $F_{11} = x + y'$ | $x \subset y$      | Implication  | If $y$ , then $x$    |  |  |

| $F_{12} = x'$     | <i>x</i> ′         | Complement   | Not x                |  |  |

| $F_{13} - x' + y$ | $x \supset y$      | Implication  | If x, then y         |  |  |

| $F_{14} = (xy)'$  | $x \uparrow y$     | NAND         | Not-AND              |  |  |

| $F_{15} = 1$      |                    | Identity     | Binary constant 1    |  |  |

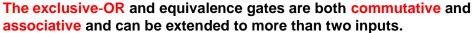

## **Logic Gates**

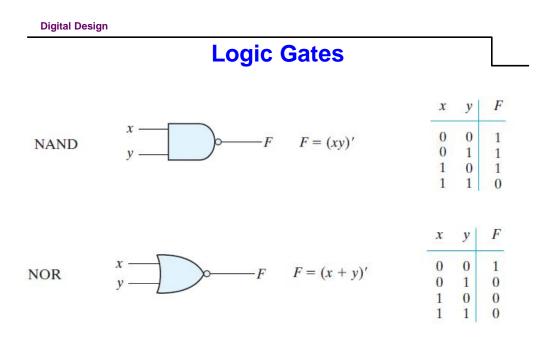

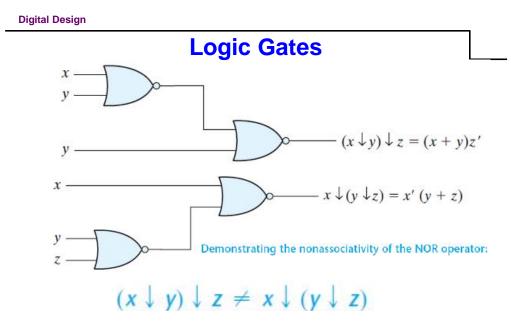

### The NAND and NOR operators are not associative

$$(x \downarrow y) \downarrow z = [(x + y)' + z]' = (x + y)z' = xz' + yz'$$

$$x \downarrow (y \downarrow z) = [x + (y + z)']' = x'(y + z) = x'y + x'z$$

$$x \downarrow y \downarrow z = (x + y + z)'$$

$$x \uparrow y \uparrow z = (xyz)'$$

Dr. Hany Ahmed Date: 2016

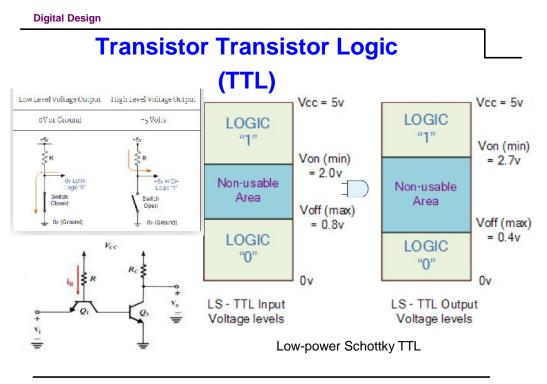

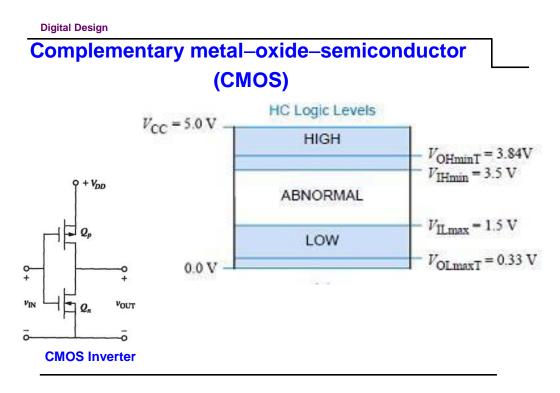

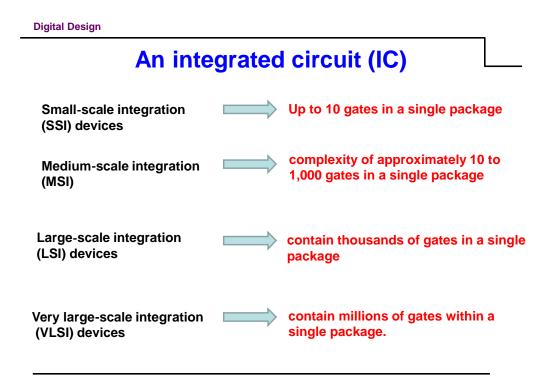

## **Logic Families**

Many different logic families of digital integrated circuits

TTL transistor-transistor logic;

ECL emitter<sup>-</sup>coupled logic; high-speed operation

**MOS** metal<sup>-</sup>oxide semiconductor; high component density

**CMOS** complementary metal<sup>-</sup>oxide semiconductor.

Low power consumption is essential for VLSI design

Dr. Hany Ahmed Date: 2016

**Digital Design**

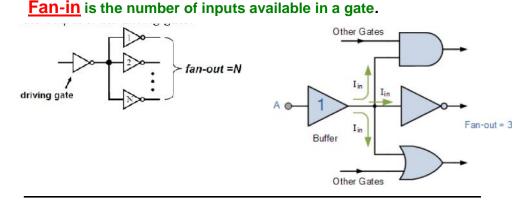

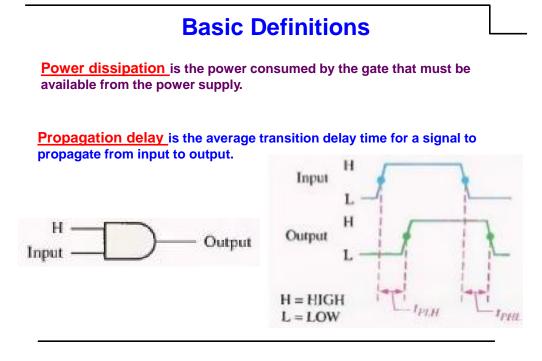

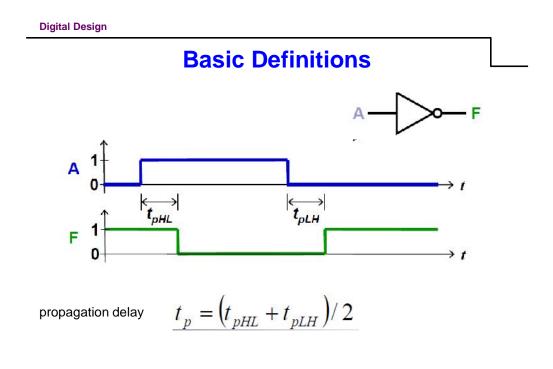

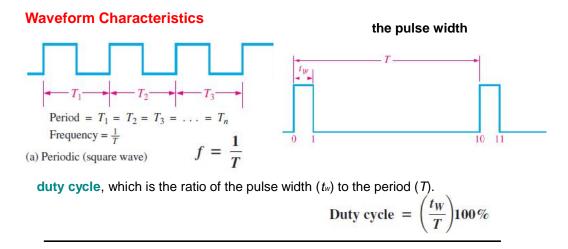

## **Basic Definitions**

**<u>Fan-out</u>** specifies the number of standard loads that the output of a typical gate can drive without impairing its normal operation.

Dr. Hany Ahmed Date: 2016

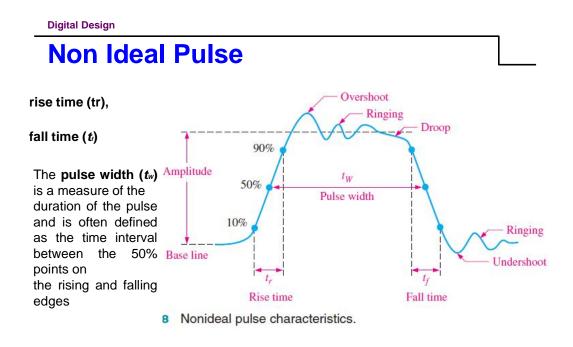

### **Standard Load and Waveform**

<u>A standard load</u> is usually defined as the amount of current needed by an input of another similar gate in the same family.

Dr. Hany Ahmed Date: 2016

Digital Design

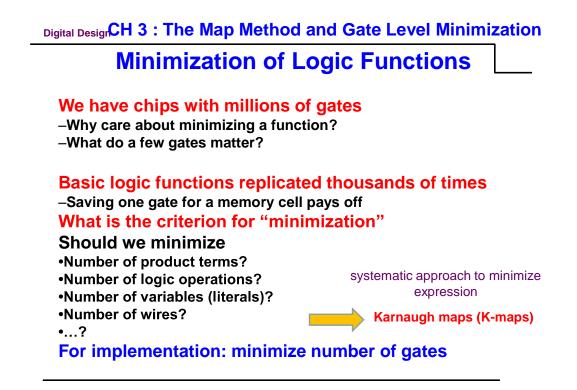

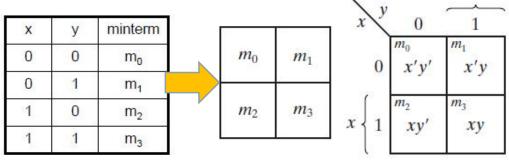

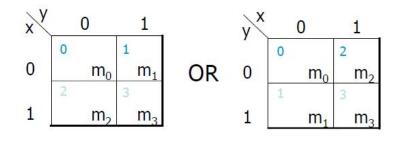

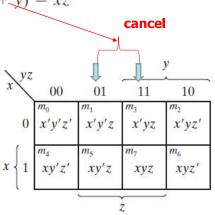

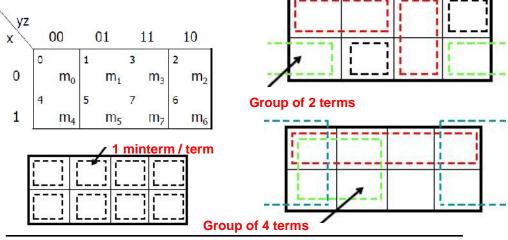

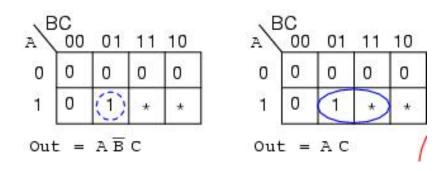

### Karnaugh Maps

• Karnaugh maps (K-maps) are *graphical* representations.

- One *map cell* corresponds to a row in the truth table.

- Also, one map cell corresponds to a minterm or a maxterm in the boolean expression

• Multiple-cell areas of the map correspond to standard terms.

## **Karnaugh Maps**

**NOTE:** ordering of variables is **IMPORTANT** for f(x,y), x is the row, y is the column. Cell 0 represents x'y'; Cell 1 represents x'y; etc.

If a minterm is present in the function, then a 1 is placed in the corresponding cell.

Dr. Hany Ahmed Date: 2016

#### **Digital Design Boolean Function in Karnaugh Map** 1s and 0s represent function in Karnaugh map -1 represent On-set (F=1), 0 represents Off-set (F=0) -Similar to truth table f f Х y х у -0s are typically not shown 0 0 0 0 0 0 0 1 0 1 0 1 **Example: And & OR Gates** 1 1 0 0 1 0 1 1 1 1 1 1 y 1 0 1 x 1 0 0 1 х 1 1 1 (b) x + y(a) xy (b) x + y

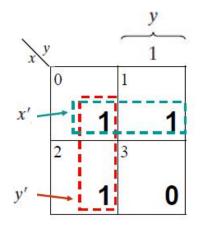

## **Boolean Function in Karnaugh Map**

F = x' + y';

Any two adjacent cells in the map differ by ONLY one variable, which appears complemented in one cell and uncomplemented in the other.

•Example: mo (=x'y') is adjacent to m1 (=x'y) this means that x'y' +x'y= x'(y'+y)=x'

•Also m<sub>0</sub> (=x'y') is adjacent to m<sub>2</sub> (=xy') x'y' +xy'= y'(x'+x)=y

Dr. Hany Ahmed Date: 2016

#### **Digital Design**

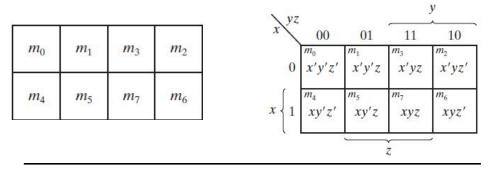

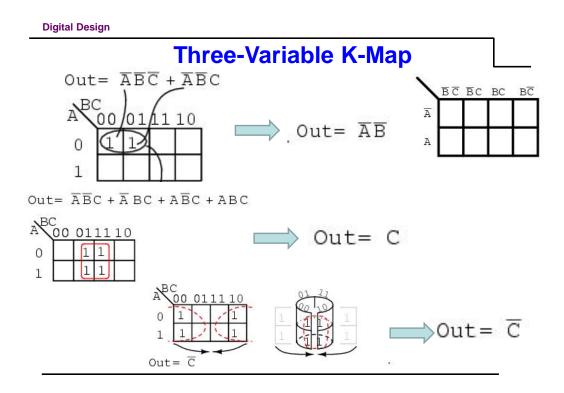

## **Three-Variable K-Map**

• Karnaugh map with 3 variables:

- Two variables on one side, one on the other

- Note Gray code sequence (single variable change) facilitates grouping of 1-entries into logic blocks

• Note that the minterms are not arranged in a binary sequence, but similar to the Gray code.

• For simplifying Boolean functions, we must recognize the basic property possessed by adjacent squares.

Dr. Hany Ahmed Date: 2016

### **Three-Variable K-Map**

To clarify this concept, consider the sum of two adjacent squares such as  $m_{\rm b}$  and  $m_{\rm c}$ :

$m_5 + m_7 = xy'z + xyz = xz(y' + y) = xz$

Here, the two squares differ by the variable y, which can be removed when the sum of the two minterms is formed. Thus, any two minterms in adjacent squares (vertically or horizontally, but not diagonally, adjacent) that are ORed together will cause a removal of the dissimilar variable.

Neighboring minterms can be combined:

Dr. Hany Ahmed Date: 2016

#### **Digital Design**

-Note: variable ordering is (x,y,z); yz specifies column, x specifies row. -Each cell is adjacent to *three* other cells (left or right or top or bottom or edge wrap)

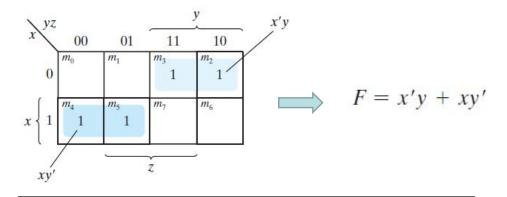

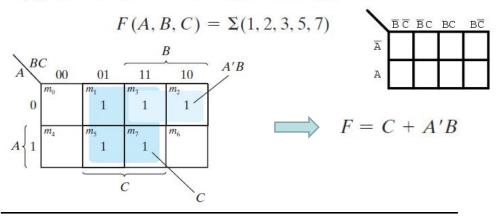

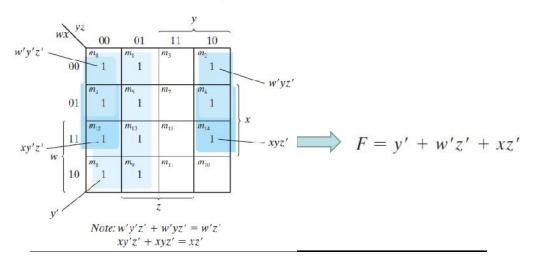

### **Three-Variable K-Map**

Simplify the Boolean function

$F(x, y, z) = \Sigma(2, 3, 4, 5)$

$F(x,y,z)=\Sigma(2,3,4,5)=x^{\prime}yz^{\prime}+x^{\prime}yz+xy^{\prime}z^{\prime}+xy^{\prime}z$

**Digital Design**

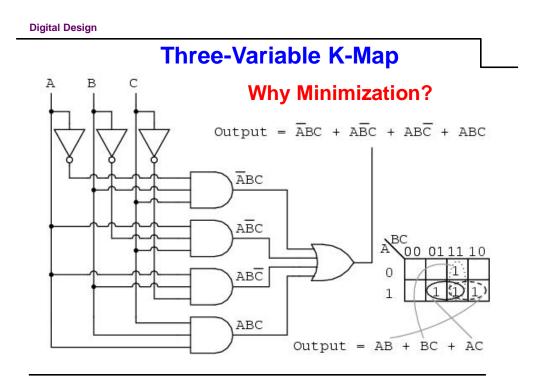

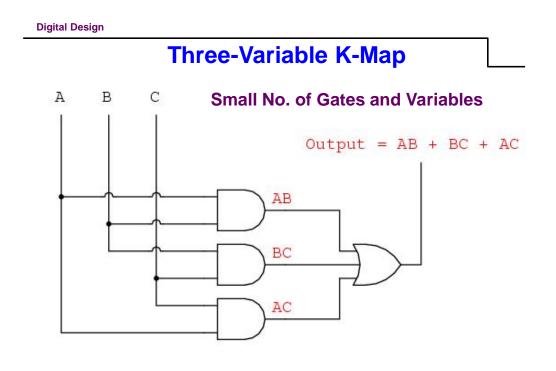

## **Three-Variable K-Map**

For the Boolean function

$$F = A'C + A'B + AB'C + BC$$

- (a) Express this function as a sum of minterms.

- (b) Find the minimal sum-of-products expression.

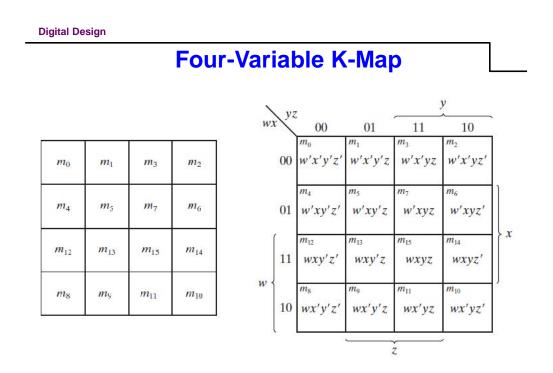

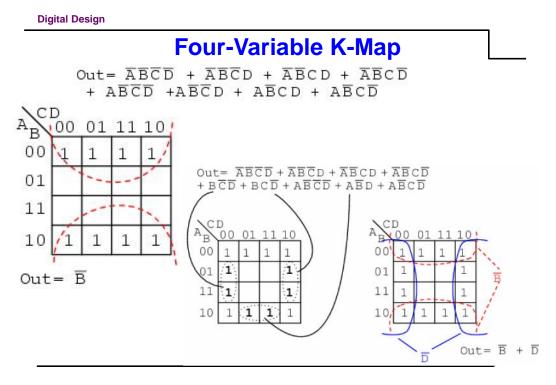

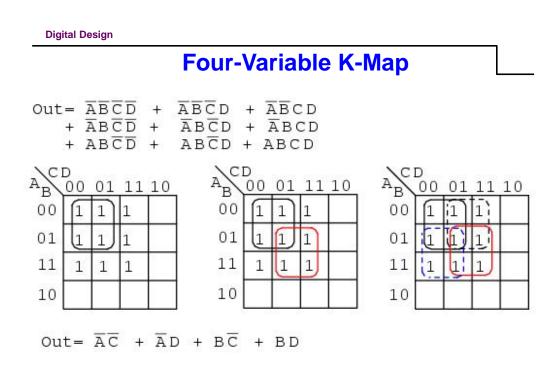

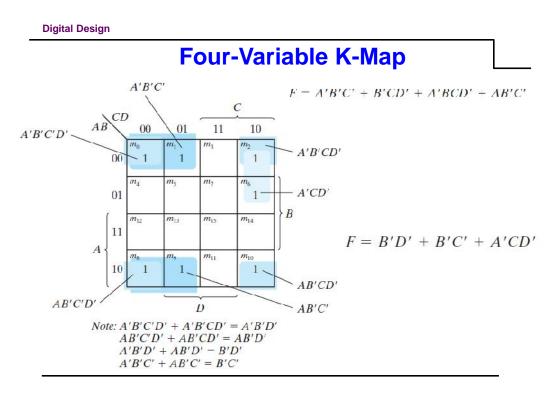

## Four-Variable K-Map

Simplify the Boolean function

$F(w, x, y, z) = \Sigma(0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$

Dr. Hany Ahmed Date: 2016

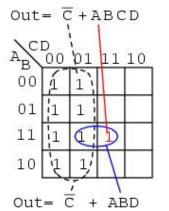

## Four-Variable K-Map

Simplification by Boolean Algebra

$Out = \overline{C} + ABCD$

Applying rule  $\mathbf{A} + \overline{\mathbf{A}}\mathbf{B} = \mathbf{A} + \mathbf{B}$  to the  $\overline{\mathbf{C}}$  + ABCD term

$Out = \overline{C} + ABD$

Dr. Hany Ahmed Date: 2016

Dr. Hany Ahmed Date: 2016

**Digital Design**

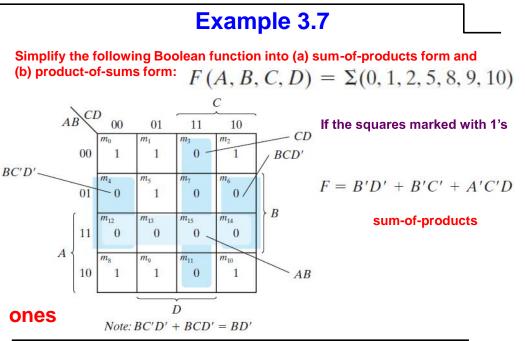

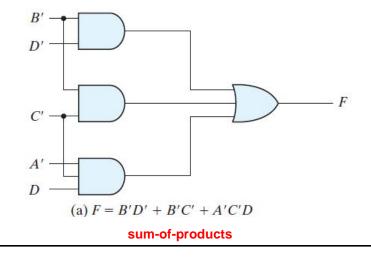

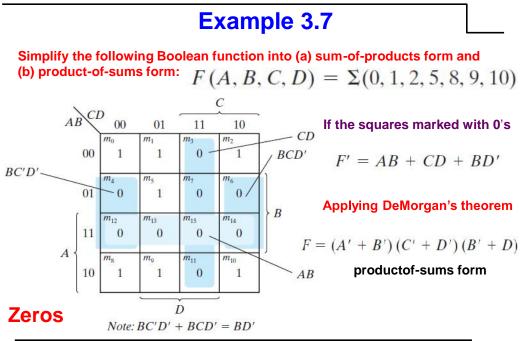

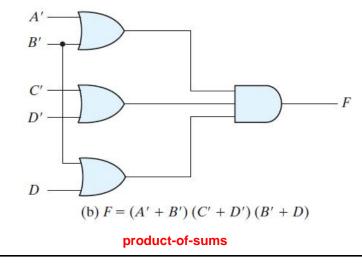

Example 3.7

## Simplify the following Boolean function into (a) sum-of-products form and (b) product-of-sums form:

Dr. Hany Ahmed Date: 2016

**Digital Design**

Example 3.7

Simplify the following Boolean function into (a) sum-of-products form and (b) product-of-sums form:

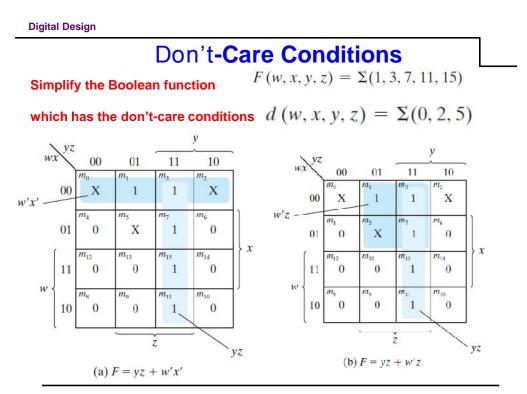

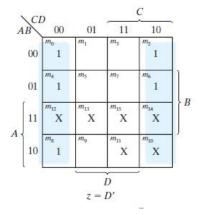

## Don't-Care Conditions

Don't Care Cells in the Karnaugh Map >>>>> x or \*

Don't cares in a Karnaugh map, or truth table, may be either 1s or 0s,

Dr. Hany Ahmed Date: 2016

#### Don't-Care Conditions

$$F(w, x, y, z) = yz + w'x' = \Sigma(0, 1, 2, 3, 7, 11, 15)$$

$$F(w, x, y, z) = yz + w'z = \Sigma(1, 3, 5, 7, 11, 15)$$

It is also possible to obtain a simplified product-of-sums expression for the function. In this case, the only way to **combine the 0's** is to include don't-care minterms 0 and 2 with the 0's to give a simplified complemented function:

$$F' = z' + wy'$$

$$F(w, x, y, z) = z(w' + y) = \Sigma(1, 3, 5, 7, 11, 15)$$

Dr. Hany Ahmed Date: 2016

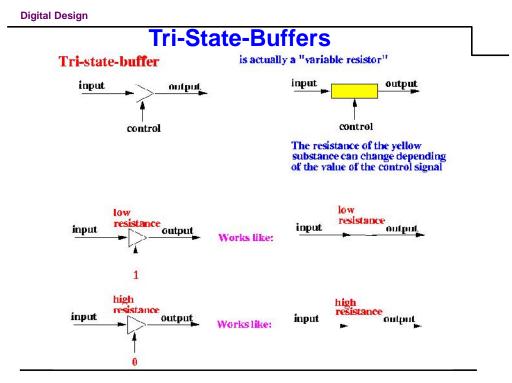

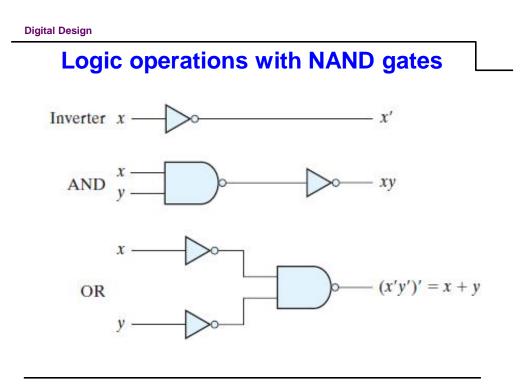

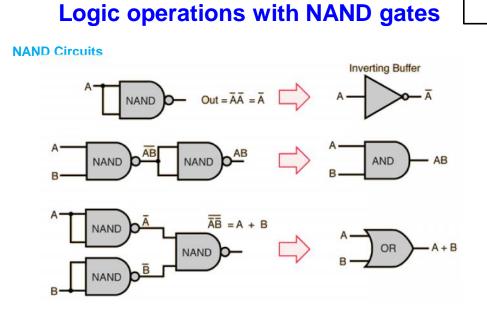

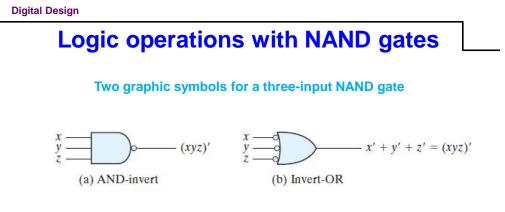

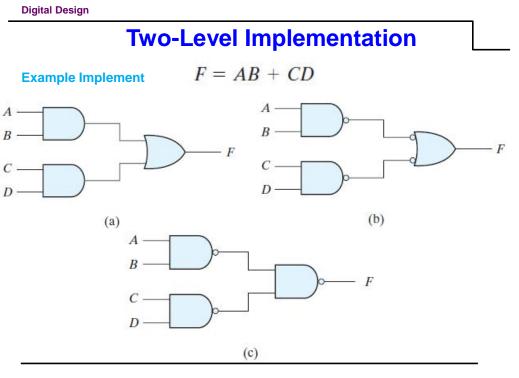

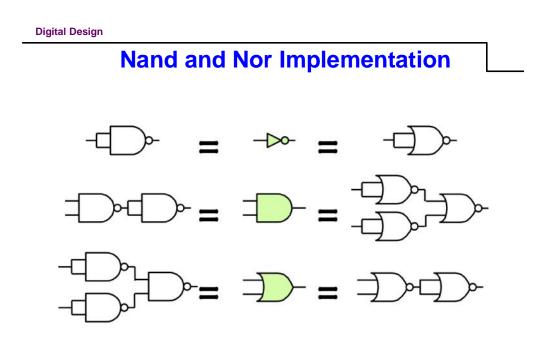

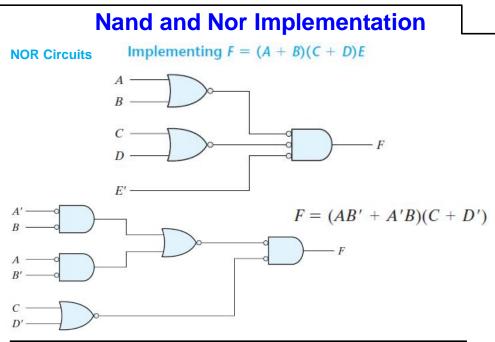

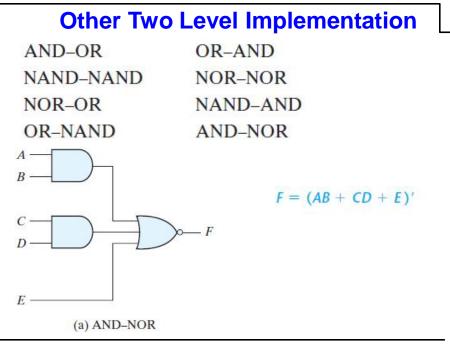

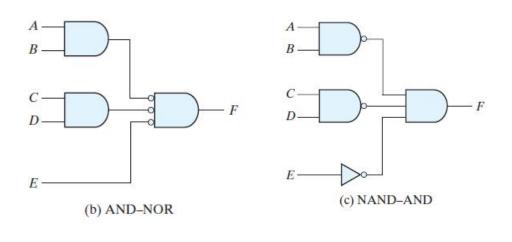

#### Digital Design CH 3 Nand and Nor Implementation

#### Nand and Nor Implementation

- Digital circuit are frequently constructed with NAND or NOR gates rather than AND and OR gates.

- NAND and NOR gates are easier to fabricate with electronic

components and are the basic gates used in all IC digital logic families.

Dr. Hany Ahmed Date: 2016

The implementation of Boolean functions with NAND gates requires that the functions be in sum-of-products form.

#### **Digital Design**

# Logic operations with NAND gates

Implement the following Boolean function with NAND gates:

$$F(x, y, z) = (1, 2, 3, 4, 5, 7)$$

# Logic operations with NAND gates

Implement the following Boolean function with NAND gates:

$$F = xy' + x'y + z$$

Dr. Hany Ahmed Date: 2016

#### Digital Design

F = (AB + CD + E)'

#### **Nand and Nor Implementation**

**Example**

F' = x'y + xy' + zF = (x'y + xy' + z)'

Dr. Hany Ahmed Date: 2016

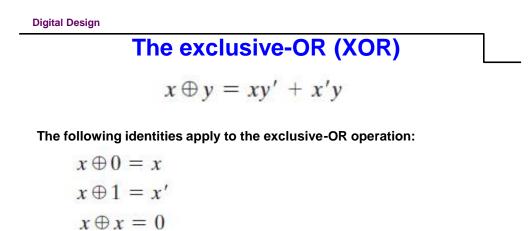

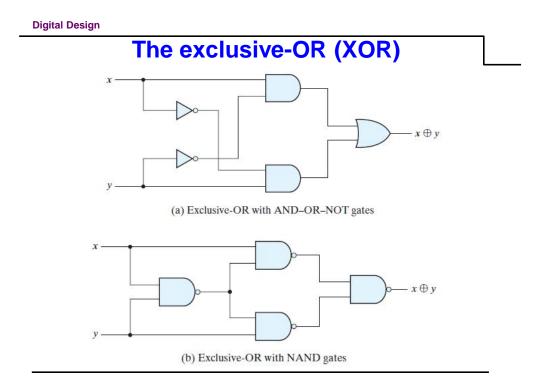

$x \oplus x' = 1$

$x \oplus y' = x' \oplus y = (x \oplus y)'$

the exclusive-OR operations both commutative and associative;

$$A \oplus B = B \oplus A$$

and

$(A \oplus B) \oplus C = A \oplus (B \oplus C) = A \oplus B \oplus C$

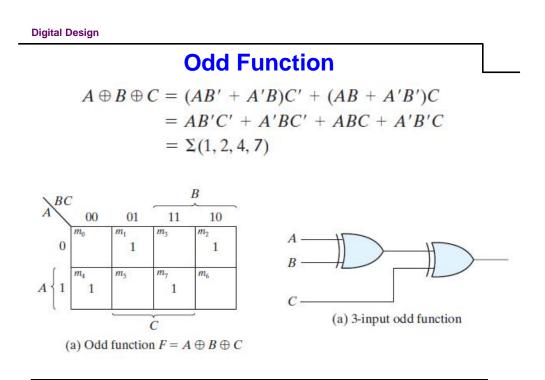

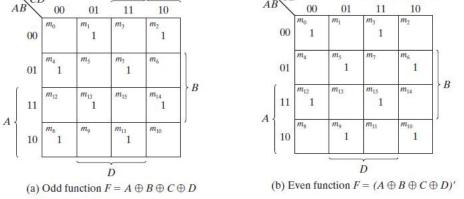

# Odd Function $A \oplus B \oplus C \oplus D = (AB' + A'B) \oplus (CD' + C'D)$ = (AB' + A'B)(CD + C'D') + (AB + A'B')(CD' + C'D) $= \Sigma(1, 2, 4, 7, 8, 11, 13, 14)$ $AB \xrightarrow{CD} 00 \quad 01 \quad 11 \quad 10$ $AB \xrightarrow{CD} 00 \quad 01 \quad 11 \quad 10$

Dr. Hany Ahmed Date: 2016

#### **Digital Design Parity Generation and Checking Even-Parity-Generator Truth Table** $P = x \oplus y \oplus z$ Three-Bit Message **Parity Bit** P X y Z Ζ. (a) 3-bit even parity generator Even Parity Check → 1- No. of One's Even → 0 2- No. of One's Odd→ 1

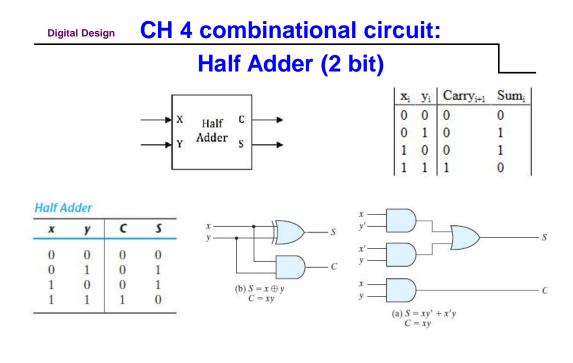

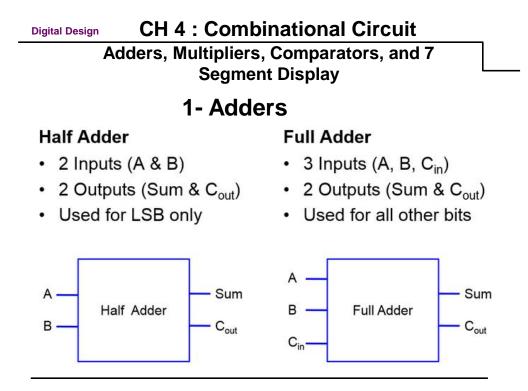

#### **CH 4 combinational circuit:**

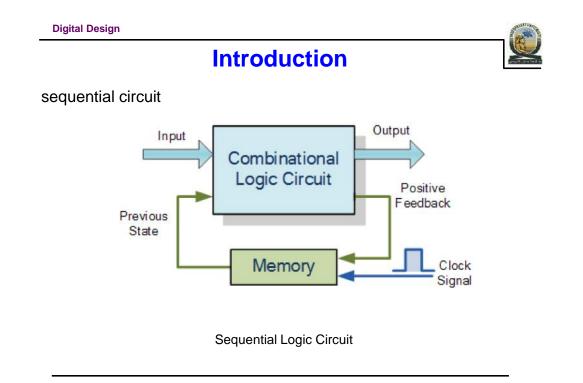

Logic circuits can be classified as either

1- Combinational Logic Circuits — the output(s) depend only on the input(s) at any specific time and not on any previous input(s).

An example of the two concepts is a television remote control. You can enter a number and the output (a particular television channel) depends only on the number entered. It does not matter what channels been viewed previously. So the relationship between the input (a number) and the output is combinational.

# 2- Sequential Logic Circuits — the output(s) depend both on previous and current input(s).

The remote control also has inputs for stepping either up or down one channel. When using this input method, the channel selected depends on what channel has been previously selected and the sequence of up/down button pushes. The channel up/down buttons illustrate a sequential input/output relationship.

Dr. Hany Ahmed Date: 2016

**Digital Design**

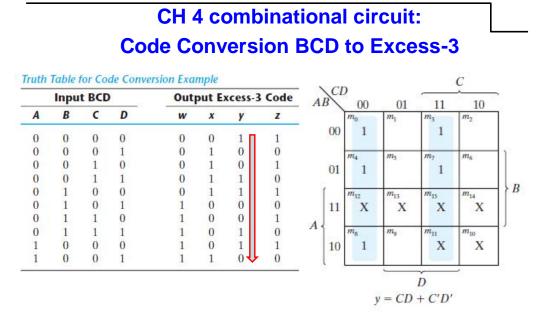

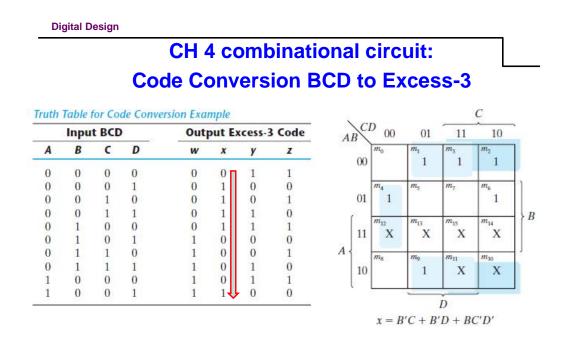

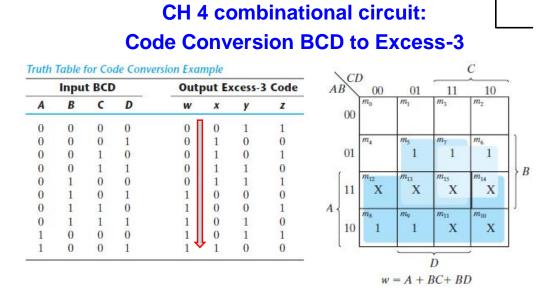

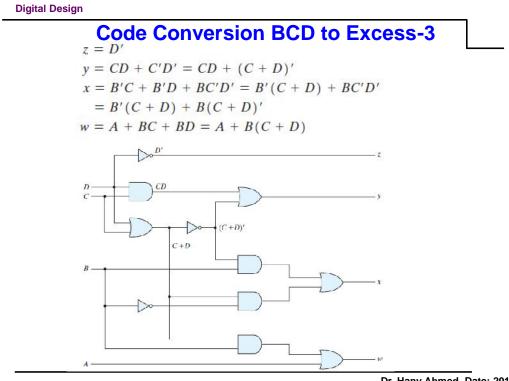

#### CH 4 combinational circuit: Code Conversion BCD to Excess-3

|   | Inpu | t BCD | ) | <b>Output Excess-3 Cod</b> |   |   |   |  |  |  |  |

|---|------|-------|---|----------------------------|---|---|---|--|--|--|--|

| Α | В    | С     | D | w                          | x | y | z |  |  |  |  |

| 0 | 0    | 0     | 0 | 0                          | 0 | 1 | 1 |  |  |  |  |

| 0 | 0    | 0     | 1 | 0                          | 1 | 0 | 0 |  |  |  |  |

| 0 | 0    | 1     | 0 | 0                          | 1 | 0 | 1 |  |  |  |  |

| 0 | 0    | 1     | 1 | 0                          | 1 | 1 | 0 |  |  |  |  |

| 0 | 1    | 0     | 0 | 0                          | 1 | 1 | 1 |  |  |  |  |

| 0 | 1    | 0     | 1 | 1                          | 0 | 0 | 0 |  |  |  |  |

| 0 | 1    | 1     | 0 | 1                          | 0 | 0 | 1 |  |  |  |  |

| 0 | 1    | 1     | 1 | 1                          | 0 | 1 | 0 |  |  |  |  |

| 1 | 0    | 0     | 0 | 1                          | 0 | 1 | 1 |  |  |  |  |

| 1 | 0    | 0     | 1 | 1                          | 1 | 0 | 0 |  |  |  |  |

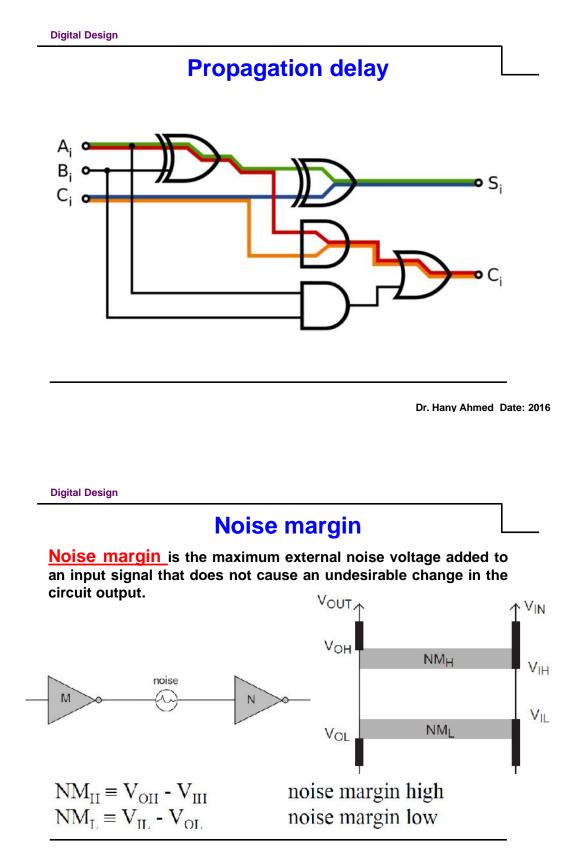

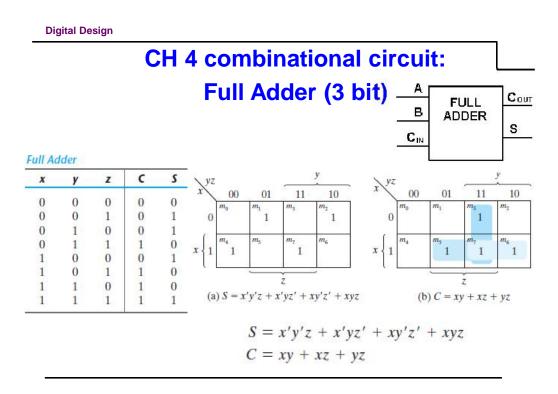

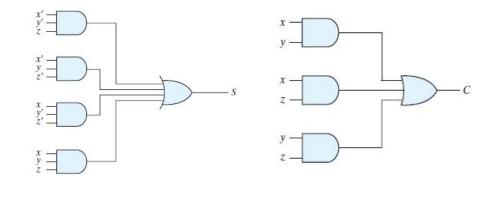

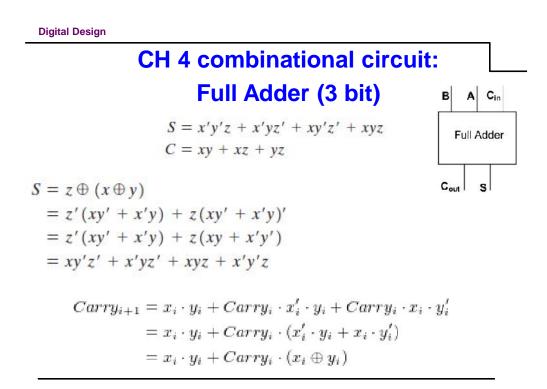

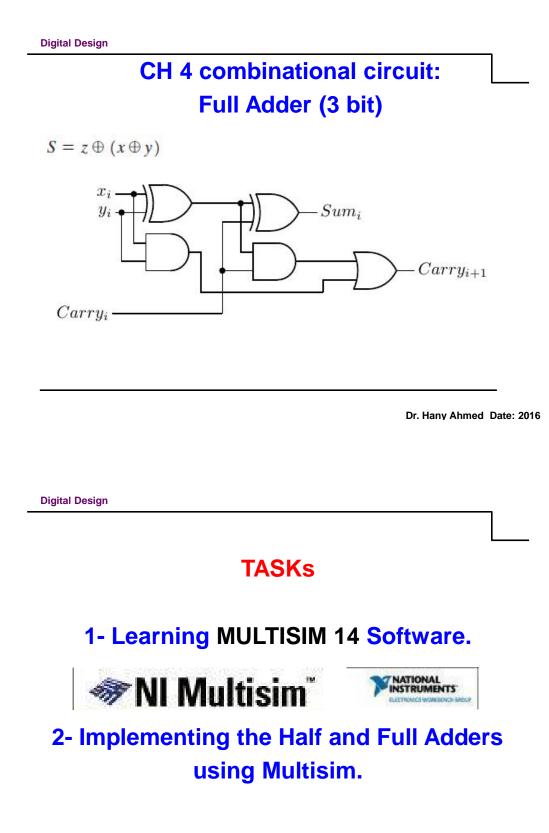

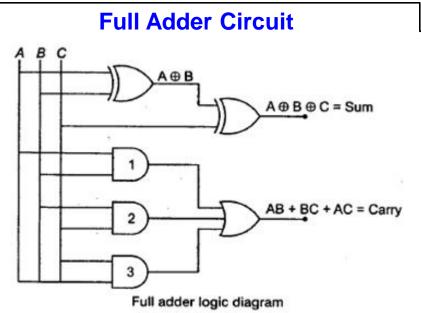

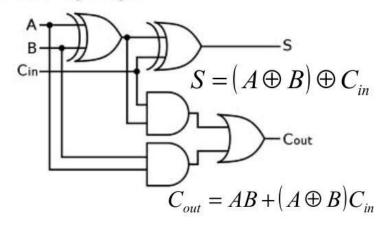

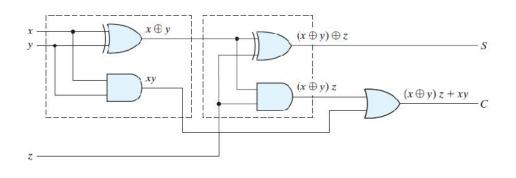

# CH 4 combinational circuit: Full Adder (3 bit)

S = x'y'z + x'yz' + xy'z' + xyzC = xy + xz + yz

Dr. Hany Ahmed Date: 2016

#### **Full Adder Circuit**

• Full adder logic diagram

Dr. Hany Ahmed Date: 2016

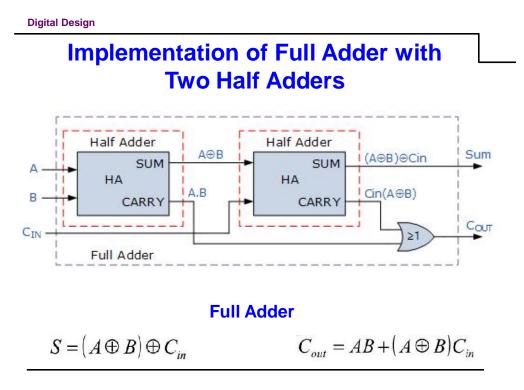

# Implementation of Full Adder with Two Half Adders

Dr. Hany Ahmed Date: 2016

#### **Digital Design**

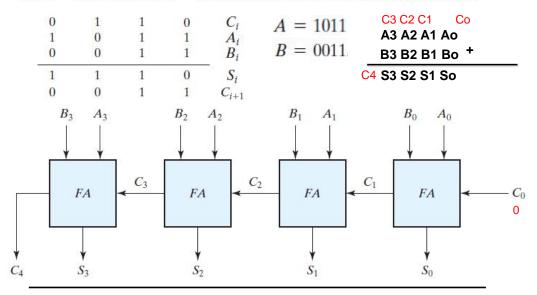

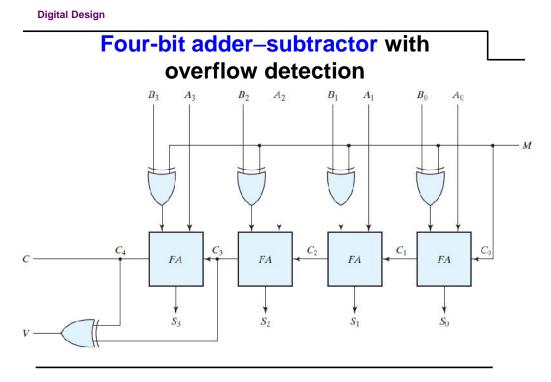

#### **Four-bit Adder**

To demonstrate with a specific example, consider the two binary numbers A = 1011and B = 0011. Their sum S = 1110 is formed with the four-bit adder as follows:

Dr. Hany Ahmed Date: 2016

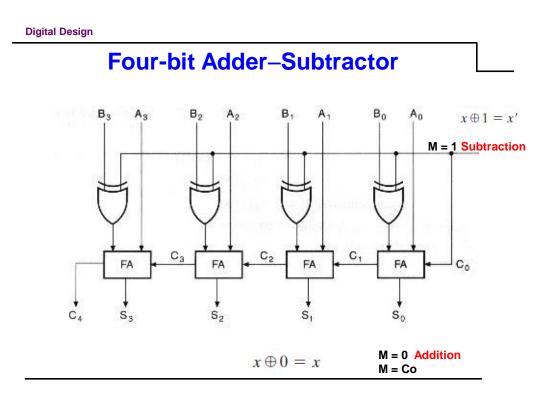

#### **Subtraction with Complements**

The subtraction of two *n*-digit unsigned numbers M - N in base *r* can be done as follows:

- 1. Add the minuend M to the r's complement of the subtrahend N. Mathematically,  $M + (r^n - N) = M - N + r^n$ .

- 2. If  $M \ge N$ , the sum will produce an end carry  $r^n$ , which can be discarded; what is left is the result M N.

- 3. If M < N, the sum does not produce an end carry and is equal to  $r^n (N M)$ , which is the *r*'s complement of (N M). To obtain the answer in a familiar form, take the *r*'s complement of the sum and place a negative sign in front.

The following examples illustrate the procedure:

Dr. Hany Ahmed Date: 2016

**Digital Design**

#### **Subtraction with Complements**

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a) X - Y and (b) Y - X by using 2's complements.

(a) X = 1010100 84 2's complement of Y = + 0111101 67 Sum = 10010001 Discard end carry  $2^7 = -10000000$ Answer: X - Y = 0010001 17

### **Subtraction with Complements**

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a) X - Y and (b) Y - X by using 2's complements.

(b)

$$Y = 1000011$$

2's complement of  $X = + 0101100$

Sum = 1101111

There is no end carry. Therefore, the answer is Y - X = -(2>s complement of 1101111) = -0010001

Dr. Hany Ahmed Date: 2016

# **Unsigned Numbers**

| C4<br>End Carry | Case<br>Addition       | Case<br>Subtraction                                             |

|-----------------|------------------------|-----------------------------------------------------------------|

| 0               | Correct<br>(N) bits    | The answer is<br>negative and the 2's<br>complement<br>(N) bits |

| 1               | Overflow<br>(N+1) bits | Discard the End Carry<br>(N) bits                               |

Dr. Hany Ahmed Date: 2016

#### **Digital Design**

# **Signed Binary Numbers**

#### 1- the signed-magnitude

The representation: the sign with a bit placed in the leftmost position of the number. The convention is to make the sign **bit 0** for **positive** and **1** for **negative**.

For example, the string of bits 01001 can be considered as 9 (unsigned binary) or as +9 (signed binary)

The string of bits 11001 represents the binary equivalent of 25 when considered as an unsigned number and the binary equivalent of -9 when considered as a signed number

referred to as the signed-magnitude

#### 2- the signed-Complement system

The complement will always start with a 1, indicating a negative number. The signed-complement system can use either the 1's or the 2's complement, but the 2's complement is the most common.

there are three different ways to represent -9 with eight bits

| signed-magnitude representation: -9   | 10001001         |

|---------------------------------------|------------------|

| signed-1's-complement representation: | <u>1</u> 1110110 |

| signed-2's-complement representation: | 11110111         |

| signed-magnitude representation: +9   | 00001001         |

The representation: the sign with a bit placed in the leftmost position of the number. The convention is to make the sign **bit 0** for **positive** and **1** for **negative**.

Dr. Hany Ahmed Date: 2016

#### **Digital Design**

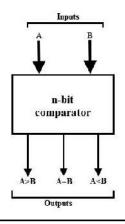

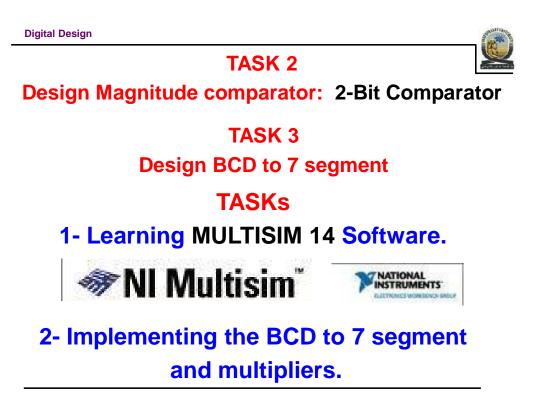

#### **Magnitude Comparator**

*magnitude comparator* is a combinational circuit that compares two numbers *A* and *B* and determines their relative magnitudes. The outcome of the comparison is specified by three binary variables that indicate whether A > B, A = B, or A < B.

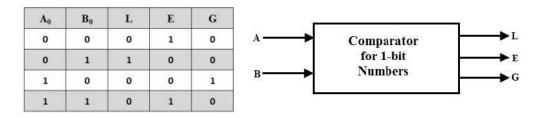

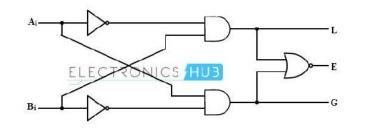

#### **Single Bit Magnitude Comparator**

A comparator used to compare two bits, i.e., two numbers each of single bit is called a single bit comparator. It consists of two inputs for allowing two single bit numbers and three outputs to generate less than, equal and greater than comparison outputs.

The truth table for the single bit comparator is given below. When A0 B0 = 00 & 11, both inputs are equal, therefore A=B output will be high. When A0 B0 = 01, B is more than A and hence AB is active.

Dr. Hany Ahmed Date: 2016

#### **Digital Design**

#### Single Bit Magnitude Comparator

| A <sub>0</sub> | B <sub>0</sub> | L | E | G |

|----------------|----------------|---|---|---|

| 0              | 0              | 0 | 1 | 0 |

| 0              | 1              | 1 | 0 | 0 |

| 1              | 0              | 0 | 0 | 1 |

| 1              | 1              | 0 | 1 | 0 |

By using these Boolean expressions, we can implement a logic circuit for this comparator using two AND gates, one NOT gate and one **Ex-NOR gate** as shown

$A0 < B0: L = \overline{A0} B0$

$A0 = B0: E = \overline{A0} \overline{B0} + A0 B0$

$A0 > B0: G = A0 \overline{B0}$

It is to be noted that E can be realized as (L+G).

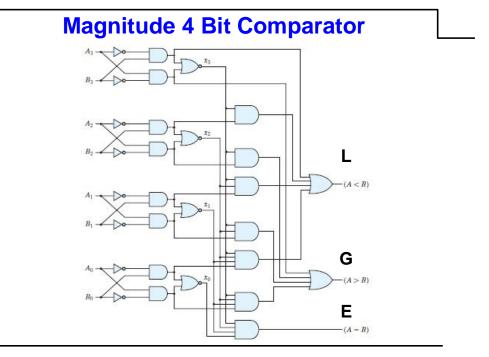

#### **Magnitude 4 Bit Comparator**

*magnitude comparator* is a combinational circuit that compares two numbers A and B and determines their relative magnitudes. The outcome of the comparison is specified by three binary variables that indicate whether A > B, A = B, or A < B.

$A = A_3 A_2 A_1 A_0$

$B = B_3 B_2 B_1 B_0$

can be expressed logically with an exclusive-NOR function as

$x_i = A_i B_i + A'_i B'_i$  for i = 0, 1, 2, 3

where  $x_i = 1$  only if the pair of bits in position *i* are equal (i.e., if both are 1 or both are 0).

Dr. Hany Ahmed Date: 2016

**Digital Design**

#### Magnitude 4 Bit Comparator

E: Equal

$(A=B)=x_3x_2x_1x_0$

#### **G:** Greater

$$(A > B) = A_3B'_3 + x_3A_2B'_2 + x_3x_2A_1B'_1 + x_3x_2x_1A_0B'_0$$

#### L: Less Than

$(A < B) = A'_{3}B_{3} + x_{3}A'_{2}B_{2} + x_{3}x_{2}A'_{1}B'_{1} + x_{3}x_{2}x_{1}A'n_{0}B'_{0}$

Dr. Hany Ahmed Date: 2016

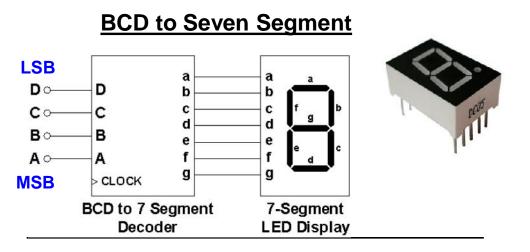

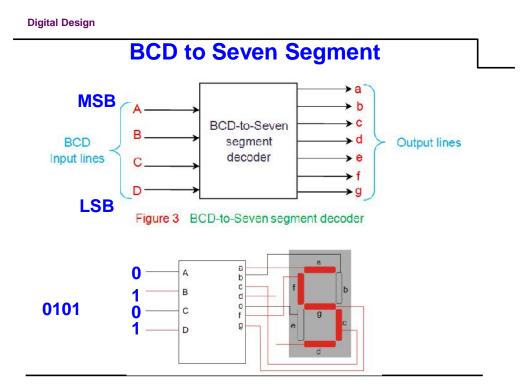

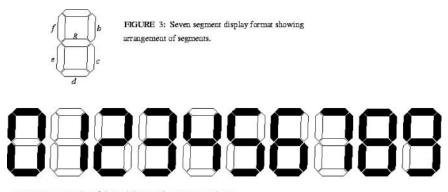

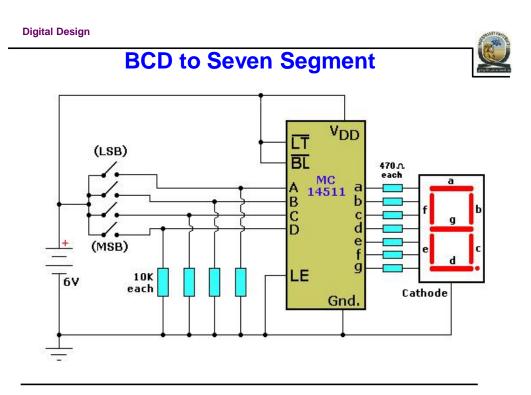

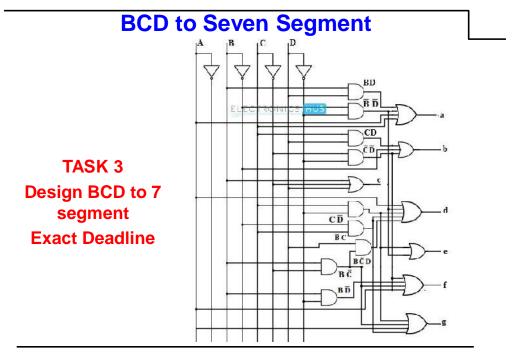

#### **7 Segment Display and Decoders**

Dr. Hany Ahmed Date: 2016

# **BCD to Seven Segment**

FIGURE 4 : Display of decimal digits with a 7-segment device.

Dr. Hany Ahmed Date: 2016

#### **Digital Design**

| ecimal | Input lines |   |   |   | 8 | ( | Display |   |   |   |   |         |

|--------|-------------|---|---|---|---|---|---------|---|---|---|---|---------|

| Digit  | Α           | В | С | D | a | b | С       | d | е | f | g | pattern |

| 0      | 0           | 0 | 0 | 0 | 1 | 1 | 1       | 1 | 1 | 1 | 0 | 8       |

| 1      | 0           | 0 | 0 | 1 | 0 | 1 | 1       | 0 | 0 | 0 | 0 | 8       |

| 2      | 0           | 0 | 1 | 0 | 1 | 1 | 0       | 1 | 1 | 0 | 1 | 8       |

| 3      | 0           | 0 | 1 | 1 | 1 | 1 | 1       | 1 | 0 | 0 | 1 | 8       |

| 4      | 0           | 1 | 0 | 0 | 0 | 1 | 1       | 0 | 0 | 1 | 1 | 8       |

| 5      | 0           | 1 | 0 | 1 | 1 | 0 | 1       | 1 | 0 | 1 | 1 | S       |

| 6      | 0           | 1 | 1 | 0 | 1 | 0 | 1       | 1 | 1 | 1 | 1 | 8       |

| 7      | 0           | 1 | 1 | 1 | 1 | 1 | 1       | 0 | 0 | 0 | 0 | 8       |

| 8      | 1           | 0 | 0 | 0 | 1 | 1 | 1       | 1 | 1 | 1 | 1 | 8       |

| 9      | 1           | 0 | 0 | 1 | 1 | 1 | 1       | 1 | 0 | 1 | 1 | 9       |

|         |   |     | 1   | le 2. | 4.2               |   |   |   |   |   |   |  |

|---------|---|-----|-----|-------|-------------------|---|---|---|---|---|---|--|

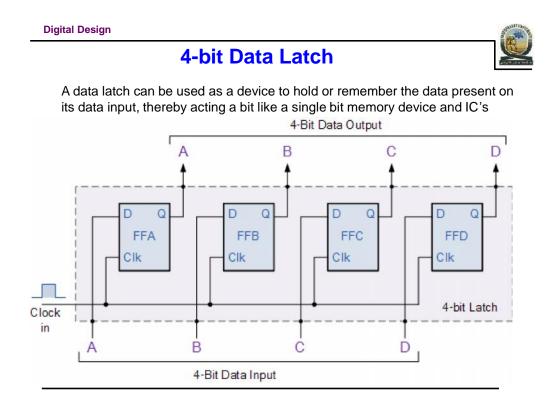

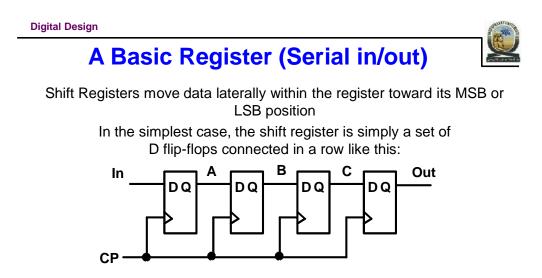

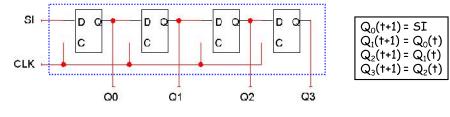

| Decimal | B | CDI | npu | its   | 7 Segment Outputs |   |   |   |   |   |   |  |